oo oo oo 20230824

OO ,oOOo. oOOooo oOOooo ,oOOo. ,oOOOo

OO OO OO OO OO OO OO OO.. THIS IS FICTITIOUS, FROM FICTIONAL PERSONA, NO IDENTIFICATION WITH ACTUAL

OO. OO OO OO. OO. OO"""' `"""OO PEOPLE|PRODUCTS|EMPLOYERS|BUSINESSES IS INTENDED OR SHOULD BE INFERRED

`Ooooo `OooO' `Oooo `Oooo `Ooooo ooooO' SPAM HOLE: FIRST AND LAST NAME JOINED WITHOUT A SPACE AT PROTONMAIL.COM

________________________________________________________________________________________________________________________________

[SPC]

IN PROGRESS ...

________________________________________________________________________________________________________________________________

[SPC] Page Faults & BO Alloc

Post on the mechanics of CPU/GPU communication. Using AMDgpu based timing results on the SteamDeck an example,

but relating to the larger picture of PC GFX APIs like Vulkan/etc.

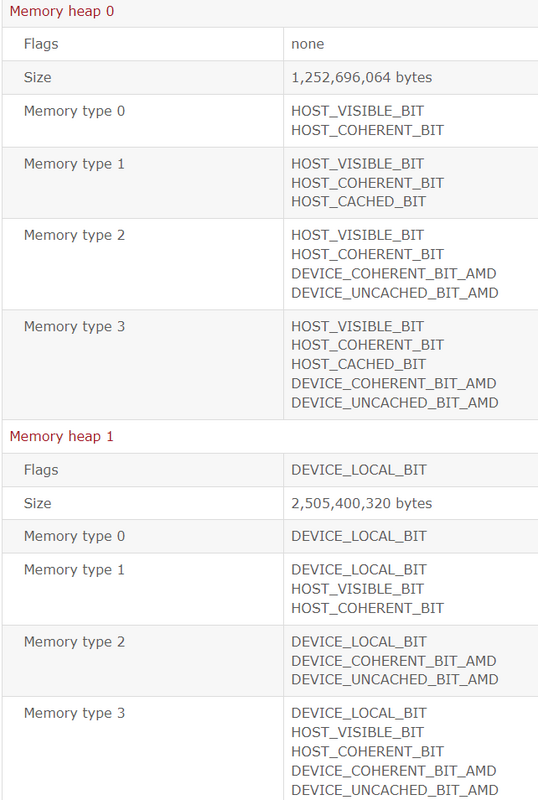

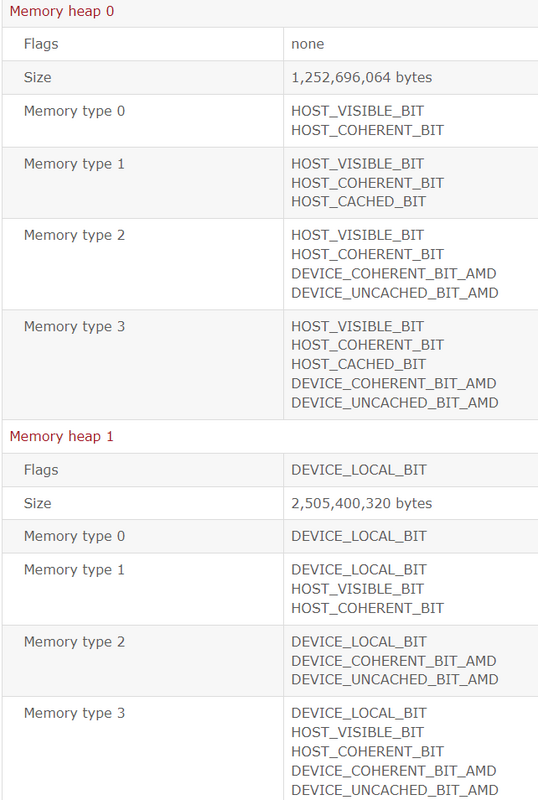

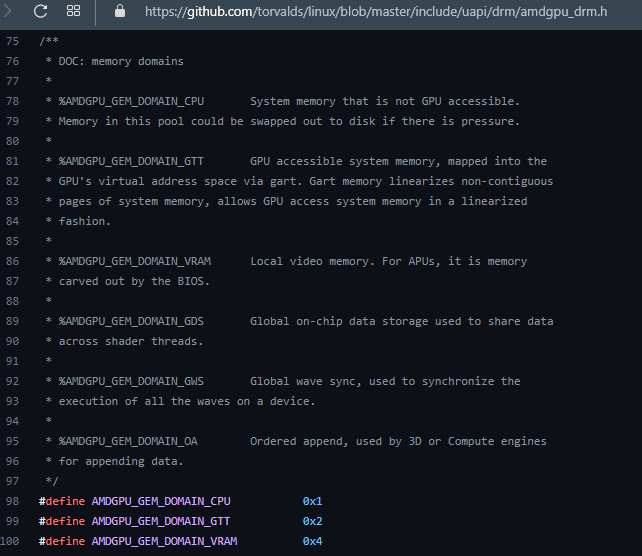

Both RADV and AMDVLK: Flush/invalidate mapped memory ranges is a NOP.

So bus-crossing dGPU traffic to HOST_VISIBLE is automatically snooping CPU caches.

The one without HOST_CACHED, is Write+Combined [WC] on store, and Uncached [UC] on read.

The one with HOST_CACHED is non-WC/UC.

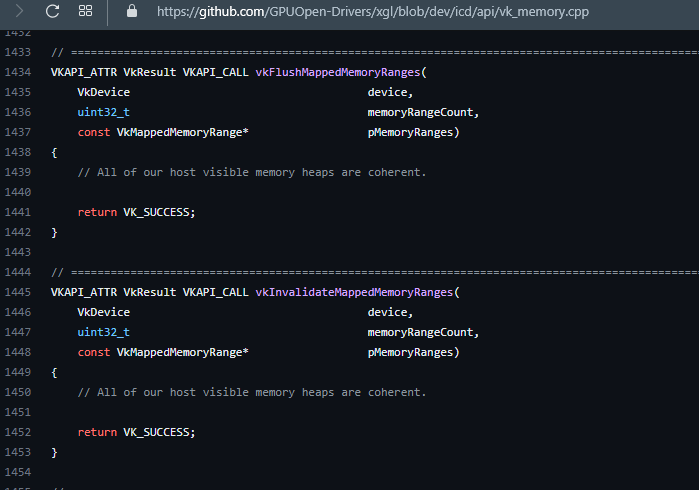

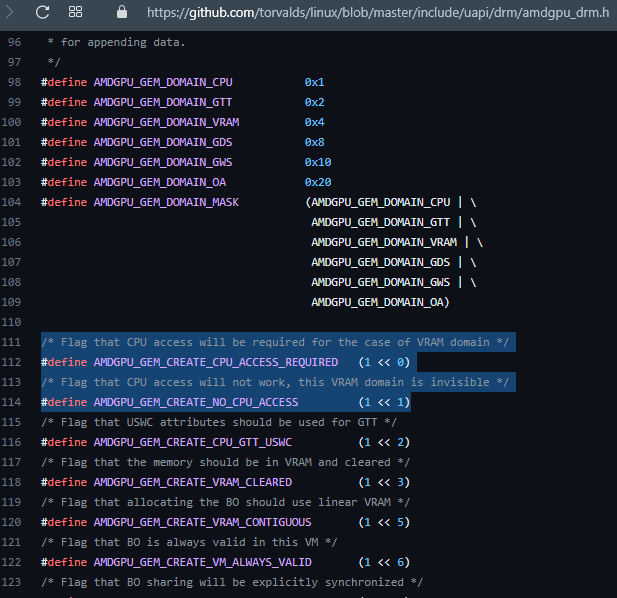

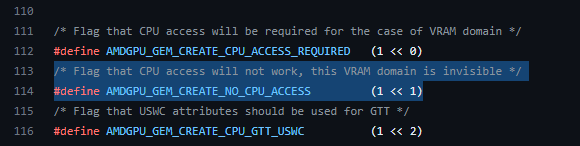

In AMDgpu (the kernel driver), likely DEVICE_LOCAL maps to AMDGPU_GEM_DOMAIN_VRAM (also the carve out on APUs)

and the non-DEVICE_LOCAL maps to AMDGPU_GEM_DOMAIN_GTT.

AMD+RADV added {DEVICE_COHERENT_BIT_AMD,

DEVICE_UNCACHED_BIT_AMD} variations to the core 4 memory types. Likely to support GPU crash debug.

But also provides a way to avoid needing to write-back (flush) GPU caches before CPU read.

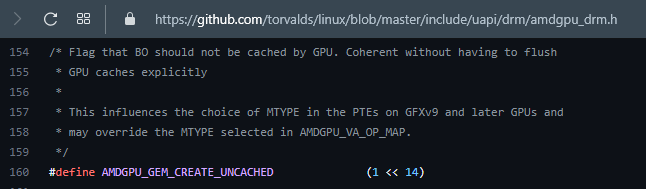

Likely AMDgpu kernel flag mapping below.

This AMDGPU_GEM_CREATE_CPU_GTT_USWC appear to toggle on WriteCombine [WC] for CPU store,

and Uncached [US] for CPU reads (cases of HOST_VISIBLE without HOST_CACHED).

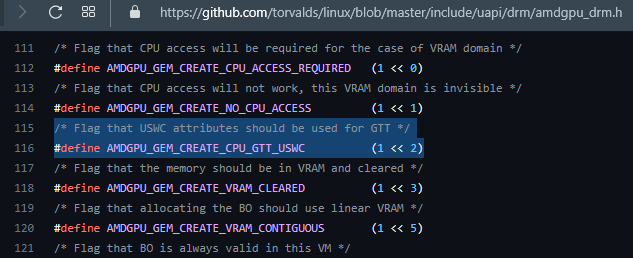

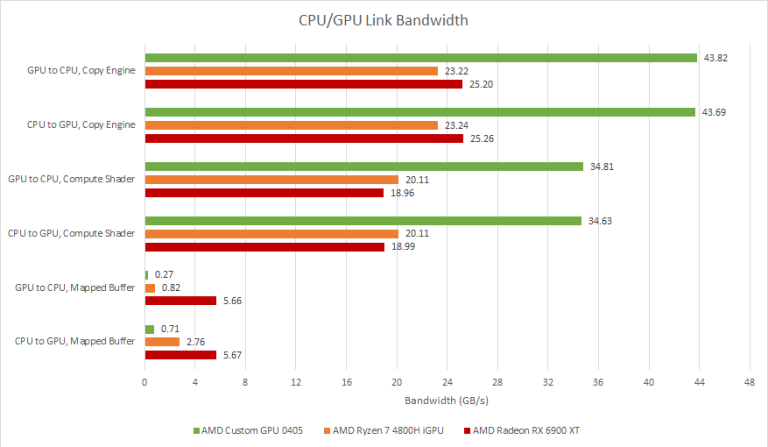

For review from ChipsAndCheese

Deck bandwidths: ~71 GB/s GPU, ~43 GB/s DMA, ~34 GB/s shader copy CPU<->GPU, ~25 GB/s CPU/CPU, and damn,

brutal 0.27 GB/s CPU mapped GPU buffer reads, 0.71 GB/s CPU mapped GPU buffer writes.

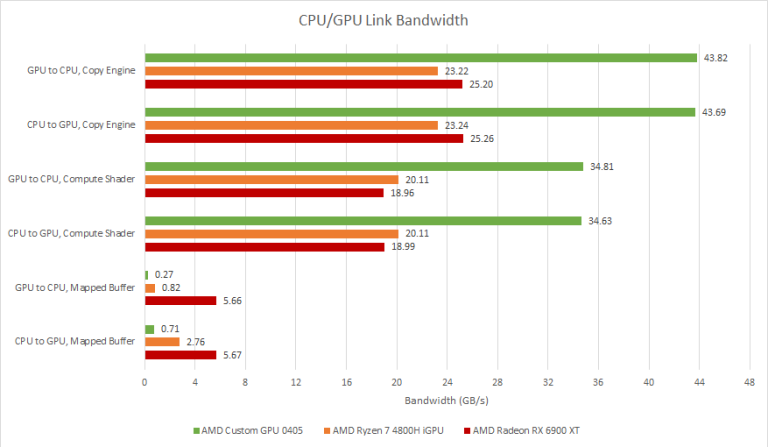

And going direct to AMDgpu instead of VK on the Deck shows these kinds of bandwidths

(non-DEVICE_LOCAL, HOST_VISIBLE with HOST_CACHED and without).

So using Write-Combined is amazingly painful for stores.

Tangental Notes

- Implies that the choices one might make on dGPU PC don't necessarily port over to APUs at all. Another challenge: it takes almost 7 seconds to zero-fill using a 64-bit store for() loop the 8-GiB of mapped memory. Hints at why load times are such a challenge even in the best case.

- This all hints at why PC OS derived systems are lacking in stuffing GPU VRAM. Really need some kind of bus mastered DMA (zero-copy) between non-volatile storage (disk) and GPU DRAM to avoid this CPU-touching performance tax.

- Or for an APU, a way to have the storage device write direct to DRAM in pages setup for use on the GPU, because anything the CPU writes that the GPU reads is stuck on the strangled snooping bus or the strangled WC buffer limit on store.

- If the app tried to manage GPU memory oversubscription via these strangled CPU mappings you'd literally see many second stalls. One can only assume the kernel can do storage<->DRAM DMA for managing GPU DRAM oversubscription?

- Even if could fill VRAM in 1 sec, just 2x oversubscription of VRAM implies 1 sec delay to context switch (assuming 2 apps accessing all meM). So classic VM multitasking is useless. Only single app focus model with pinned memory makes any useful sense. Release pin on focus change.

- The trend is massive res massive VRAM paired with tiny IO bus. So the case for pinned memory and bus master transfers only grows importance as things evolve.

Back to SteamDeck Numbers

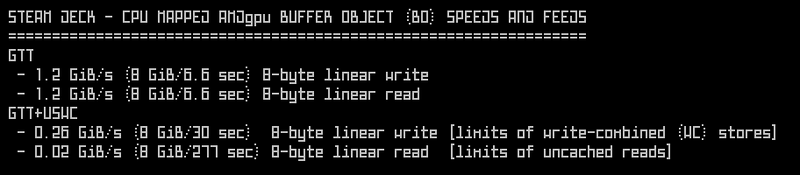

GTT (HOST_VISIBLE) + USWC (non-HOST_CACHED) takes 1 sec for 1st 4 GiB BO alloc, but *30 sec* for 2nd 4 GiB alloc. Kernel driver time for memory allocation (maybe page table related) can be brutal (general comment for PCs too).

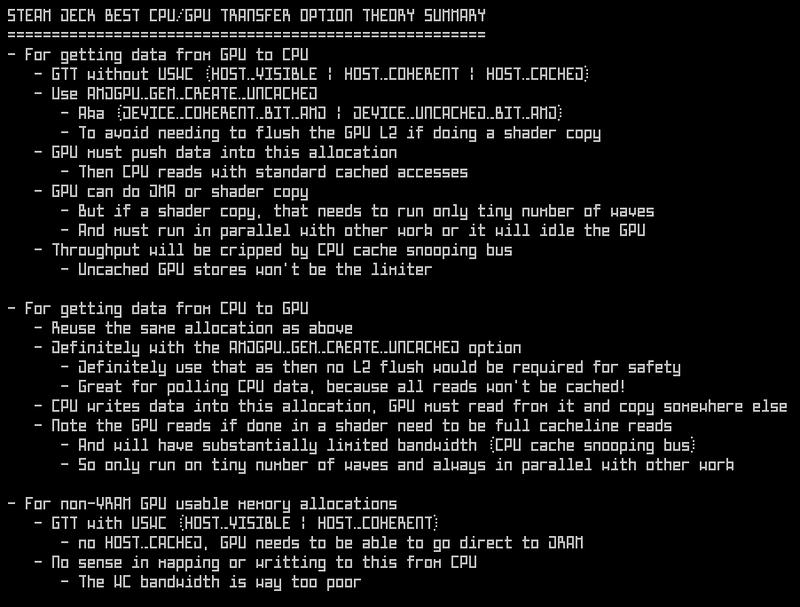

Related, I think Chips&Cheese CPU/GPU link DMA and Compute Bandwidths are only measured to a GTT+USWC buffer (only supporting useless uncached CPU reads). Bandwidth exceeds the CPU's bus capacity, implies it is 'garlic' or GPU bus only accesses, direct to DRAM.

Since RADV+AMDVLK don't support user-space CPU mapped flush | invalidate,

this implies the only supported mapping to read from DRAM direct is USWC (uncached R and write+combine W).

Doing GPU stores to a CPU mapped GTT without USWC would be crippingly slow (limited by the snooping bus rate).

But this is unfortunately the only option available for CPU read back. So if doing a shader store,

it better be only a few waves and running in parallel.

"Use GTT because it's as fast as VRAM on the Deck", could only work if GTT+USWC,

as that would be only way to get Garlic (direct to DRAM high bandwidth bus).

GTT without USWC would need Onion (slow snooping bus) because AMDgpu's only no-CPU map option is for VRAM!

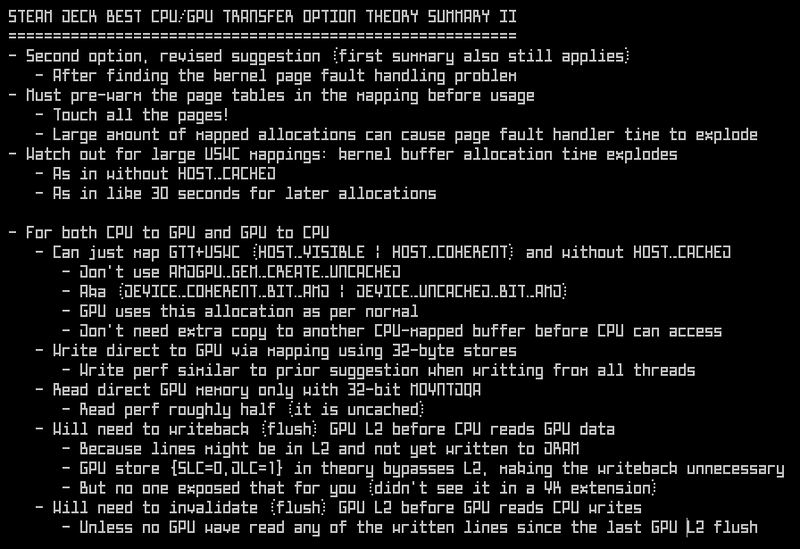

Summary of the theory on best Steam Deck practices. This is the plan for my deck-compute-only driver too.

Theory -> as in I haven't yet verified the GPU-side parts (my driver isn't that far along yet).

Possible to do better? MAYBE! CPU readback actually has 2 problems, 1st the slow GPU-side copy

(4 GiB copy via snooping bus could be almost 4 sec, but direct to DRAM via USWC might be just 160 ms).

Also CPU only has 4 MiB of L3, so the majority of 4 GiB will be uncached later.

Believe UC MTYPE (uncached) forces the CPU into serialized behavior.

My test was single thread 8-byte/access reads.

VMOVDQA_M256_YMM!

Looks like Zen2 might be able to get 32-byte/access via VMOVDQA,

and going multi-threaded (8 thread), that might be a 32x speed up.

If so might be able to approach under a GB/s for the CPU-side part (UC multithread via VMOVDQA),

which would be close enough to the non-USWC running single threaded using the cache.

What you'd really want here as a band-aid workaround is ability for the GPU to act as if the CPU map was USWC

(so go direct to DRAM), but have the CPU map act as non-USWC, so it goes through the cache.

Then some kind of hack to flush the tiny 4 MiB L3 and lower caches on the CPU.

CPU readback (reading and summing 8-byte) GTT without USWC.

- 1.16 GiB/s 1 thread

- 1.42 GiB/s 4 threads

- 1.48 GiB/s 8 threads

Going multi-core on cached readback doesn't really help much.

Proper test, parked threads waiting on futex, signal, last-1st active core timing.

Now CPU readback GTT+USWC.

- 0.13 GiB/s 4 threads 8-byte reads

- 0.24 GiB/s 8 threads 8-byte reads

- 1.15 GiB/s 8 threads 32-byte MOVNTDQA

So measurements match theory, going multi-core with MOVNTDQA uncached read

on GTT+USWC can be made to match 1 thread GTT (without USWC).

Both those results above had been using a pair of 4 GiB allocations.

The GTT+USWC one used one 4 GiB GTT+USWC for timing, and one 4 GiB GTT (unused).

And that test suffered from a 30 sec GTT BO allocation. So something was going very wrong in the page mapping.

When I rerun same test with just one 4 GiB GTT+USWC allocation, the 30 sec stall is gone, and the performance also changes.

- 18.34 GiB/s - 8 threads x 32-byte MOVNTDQA (UC)

Oh!

Perhaps there is some resource limit that kills perf if too much memory gets mapped, page faults?

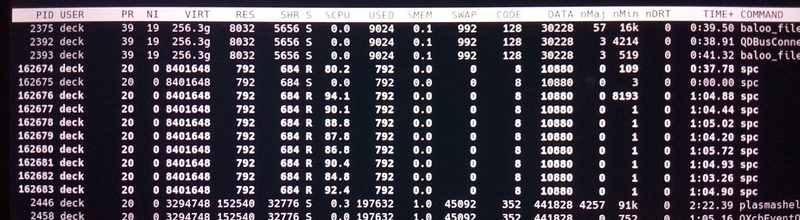

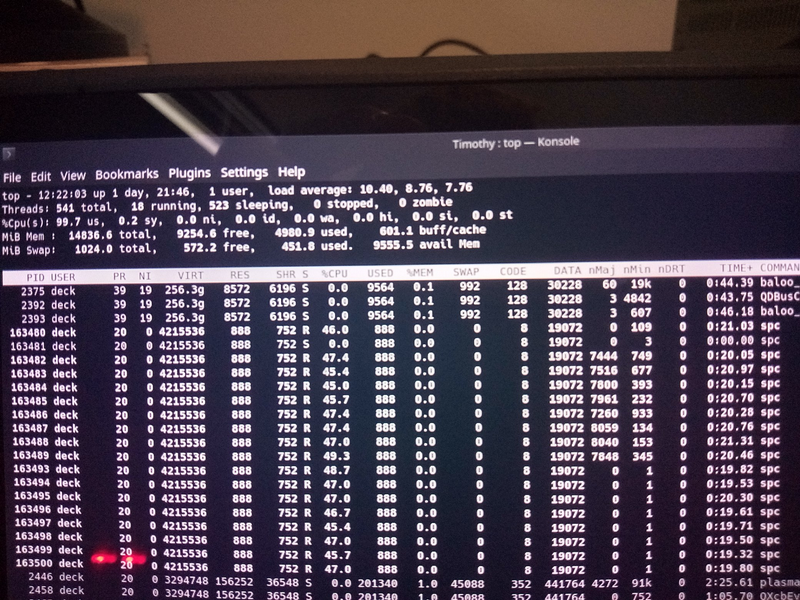

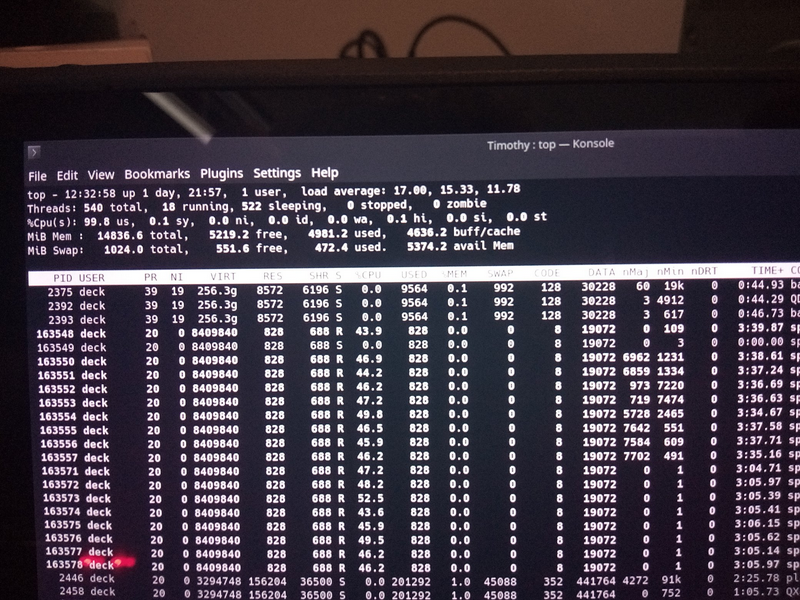

Top with thread cumulative results doesn't show anything significantly different

between the 4 GiB and 8 GiB runs in terms of page faults ... suggests it must be something else.

And yet there is obviously a bug in my multi-core tests, you can tell directly from the page fault numbers,

only one thread is taking all the faults. So it is back to finding my coding error (fail).

Lunch break and fixed the bug. Two runs now and leaving threads open to get TOP results.

First run definitely soaks up the page faults, second run is page fault free (expected). Both around only 7 GB/s.

And the 8 GiB of BO mapped, but only 4 GiB used run. The first pass gets only 1 GiB/s and the second gets 7 GiB/s.

Page fault number is similar to last run, can only conclude page fault costs exploded?

30 sec BO alloc time + super low bandwidth on 1st pass only (where page faults happen)

suggest that Linux Kernel logic explodes in cost if too many pages are used in this way.

~8K faults for 512 MiB accessed / thread = 64 KiB/fault ... X86-64 has either 4 KiB or 2 MiB for page size.

So not using large pages (fail).

Probably mapping 16 pages per fault.

Not sure if this implies anything about GPU page size (but certainly hoping it isn't 4 KiB, ouch).

Some other very rough measured numbers of GTT+USWC with 8 cores splitting 4 GiB of BO.

- ~7 GiB/s R

- ~10 GiB/s W then R

- ~15 GiB/s W

I think these seem plausable now (so maybe no more code bugs).

One takeaways of all this, is that you need to pre-warm the page tables for large mapped buffers

(by touching all pages) when the user isn't waiting on results.

And if you are doing batch jobs that {open device, send data to GPU, get data back, close device} you are screwed!

And lastly (maybe) comparison of GTT and GTT+USWC both 8 threads splitting streaming through 4 GiB of mapping (second pass, no page fault issues):

- R> ~14 GiB/s (GTT) and ~7 GiB/s (GTT+USWC)

- W+R> ~14 GiB/s (GTT) and ~10 GiB/s (GTT+USWC)

- W> ~13 GiB/s (GTT) and ~15 GiB/s (GTT+USWC)

So an alternative option summary for those who don't want the extra GPU-side GPU to CPU mapped buffer copy step.

If anyone is looking to repro the 30 sec stall: amdgpu_bo_alloc() one 4 GiB GTT+USWC, then one 4 GiB GTT buffer,

the second alloc causes the Deck to become unresponsive for 30 seconds.

Note, madvise() with MADV_HUGEPAGE on mapped 4 GiB region doesn't do anything (still faults at 64 KiB granularity),

and none of these MADV_{WILLNEED|POPULATE_READ|POPULATE_WRITE} have any effect either

(still waits until use before faulting, causing low initial effective bandwidth).

64KiB strided write through 4 GiB GTT+USWC (to pre-fault) costs the same as writing full 4 GiB, roughly 3 seconds.

So it is quite literally massive page fault overhead for 1st access.

No possible workaround found at this time for initial load time problems.

If doing two 4 GiB GTT+USWC allocations, there is also a 30 second BO allocate cost on the 2nd one.

And this makes the initial page fault cost for access to the first 4 GiB take another 30 seconds.

Effectively hangs the machine for a full minute.

Doing two 4 GiB GTT allocations (without USWC), doesn't incure any of the 30 second stalls.

So that problem is specific to big USWC allocations.

However the initial access page fault problem (extra 3 seconds) is there,

so a 2ndary problem with just mapping lots of APU memory.

Allocation of one 4 GiB GTT first then a 4 GiB GTT+USWC doesn't see the 30 second allocation stall.

Almost like anything post a big USWC alloc is poisioned.

And after mapping both, then accessing the GTT only, the 30 second time for page faulting comes back.

Even if you don't map the 2nd GTT+USWC, the 30 second initial page faulting time is still there,

so the act of mapping doesn't matter, simply doing the BO allocation had already doomed the Linux page management.

Despite header docs which imply flag only works on DOMAIN_VRAM,

using DOMAIN_GTT+AMDGPU_GEM_CREATE_NO_CPU_ACCESS is apparently what you want for non-mapped GTT allocations.

Mapped 4 GiB GTT with 4 GiB GTT+NO_CPU, drops the initial page fault time from 30 seconds to 3 sec.

________________________________________________________________________________________________________________________________

[SPC] Blame Onat

Workspace

Workspace

One day a friend Onat said to me that on Linux Steam Deck the Vulkan driver is in user space,

and it is possible to even have both RADV and the AMD Vulkan drivers running on the system at the same time ...

And That Was Enough to Seed the Idea

An idea that could not be ignored, a platform still exists,

where in theory one could ship a game with their own generated shader binary and no driver.

A way out of GPU API Hell!

This was the day I stopped my other Windows PC projects,

and became an exclusive Steam Deck developer.

________________________________

[EAT] Life of a Steak

Sometimes old technology is the best. Like when making Steaks. Salt, short dry age, season, WOOD FIRE, eat.

________________________________

[X68]

This was an idea for a simplified machine-level x86-64 interface ...

- Subset of x86-64 where instructions are always a multiple of 32-bits

- Using ignored segment override prefixes for padding

- Instructions mapped to a human readable 8-character string

Resources

Register Naming

Characters {0-9} and {A-F} reserved for hex numbers. So the 16 registers are mapped {G-V}.

_G_ _H_ _I_ _J_ _K_ _L_ _M_ _N_ _O_ _P_ _Q_ _R_ _S_ _T_ _U_ _V_

rax rcx rdx rbx rsp rbp rsi rdi r8_ r9_ r10 r11 r12 r13 r14 r15

Addressing Mode Syntax

- @u ...... [reg(u)]

- @u23 .... [reg(u)+0x23]

- @# ...... [rip+0x########], where # is the second DWORD

- @u# ..... [reg(u)+0x########]

- @uv ..... [reg(v)+reg(u)*1]

- @2uv .... [reg(v)+reg(u)*2]

- @4uv .... [reg(v)+reg(u)*4]

- @8uv .... [reg(v)+reg(u)*8]

- @4u23 ... [reg(u)*4+0x23]

- @4u# .... [reg(u)*4+0x########]

Sizing

- 'v=@u ... reg(v) = BYTE PTR [reg(u)]

- "v=@u ... reg(v) = WORD PTR [reg(u)]

- v=@u .... reg(v) = DWORD PTR [reg(u)]

- :v=@u ... reg(v) = QWORD PTR [reg(u)]

- 'v`@u ... reg(v) = sign extend BYTE PTR [reg(u)]

Maths

- v+u ... ADD (v+=u)

- v*u ... IMUL

- ~v .... NEG

- v?u ... CMP

- -v .... NEG

- v&u ... AND

- v^u ... XOR

- v=u ... MOV

- v$u ... LEA

Examples

- u+v ...... 3E4501FE ds add r14d,r15d

- u+23 ..... 4183C623 add r14d,0x23

- u+# ...... 3E4181C6 ds add r14d,0x######## ... 32-bit immediate # is next DWORD

- u*v ...... 450FAFF7 imul r14d,r15d

- ; ........ C30F1F00 ret; nop DWORD PTR [rax]

- @u=v ..... 3E45893E mov DWORD PTR ds:[r14],r15d

- @u12=v ... 45897E12 mov DWORD PTR [r14+0x12],r15d

- :u+v ..... 3E4D01FE ds add r14,r15

- :u*v ..... 4D0FAFF7 imul r14,r15

________________________________________________________________________________________________________________________________

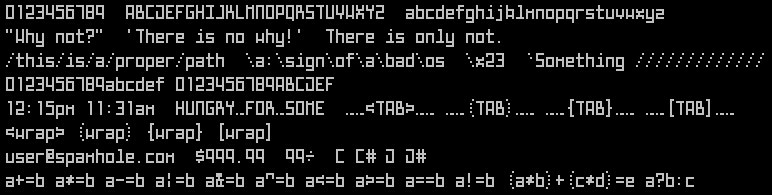

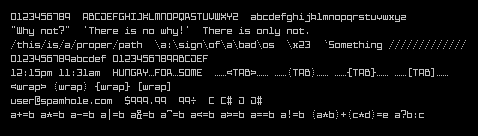

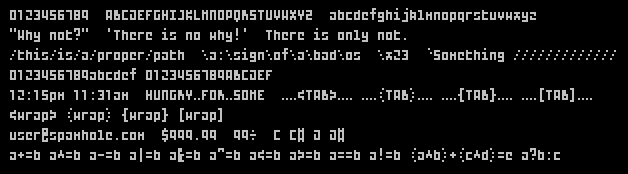

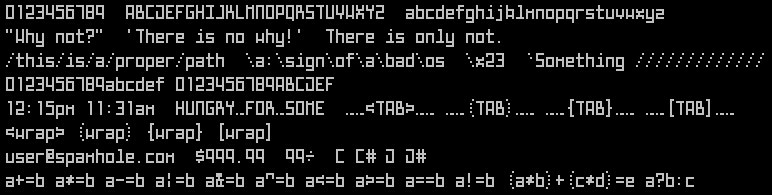

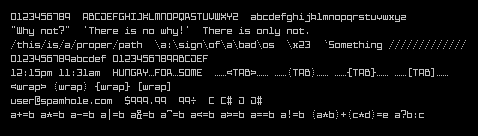

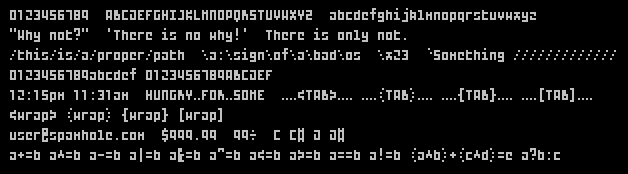

The 'Right' Font

- Only right angles, no aliasing even if scaled nearest

- X68.fon ... 5x10 character cell at 320x240 provides a 64x24 character cell screen

- X68D.fon ... Doubled size version (useful when not running on CRT)

- Made with Fony

X68 at 1:2x2

X68 at 1:2x2

X68 at 1:1

X68 at 1:1

An alternative for even smaller text? (Outtake)

At 1:2x2

At 1:2x2

At 1:1

At 1:1

________________________________________________________________________________________________________________________________

Windows/Linux ABIs

For reference...

Reviewing stack operations on x86-64.

Stack grows down, RSP points to last written entry.

- CALL rax ... rsp-=8; [rsp]=next(rip); rip=rax;

- POP rax .... rax=[rsp]; rsp+=8;

- PUSH rax ... rsp-=8; [rsp]=rax;

- RET ........ rip=[rsp]; rsp-=8;

Reviewing Windows and Linux ABI register conventions.

N X86 X68 WIN LXN

= === === === ===

0 rax g r r (return value)

1 rcx h a0 a3

2 rdx i a1 a2

3 rbx j sav sav

4 rsp k sav sav (stack pointer)

5 rbp l sav sav

6 rsi m sav a1

7 rdi n sav a0

8 r8 o a2 a4

9 r9 p a3 a5

a r10 q vol vol

b r11 r vol vol

c r12 s sav sav

d r13 t sav sav

e r14 u sav sav

f r15 v sav sav

Then the Windows stack conventions.

Anything less than RSP can be overwritten any time,

thus must move RSP before writing below a set RSP point.

Before a CALL, RSP must be 16-byte aligned.

There is a 32-byte 'shadow' region reserved for called function usage.

...

[RSP+0x28] A5

[RSP+0x20] A4

[RSP+0x18] not A3 (R9 shadow)

[RSP+0x10] not A2 (R8 shadow)

[RSP+0x08] not A1 (RDX shadow)

[RSP+0x00] not A0 (RCX shadow) ... 16-byte aligned

(return_goes_here)

Linux conventions.

...

[RSP+0x08] A7

[RSP+0x00] A6

(return_goes_here)

________________________________________________________________________________________________________________________________

Windows Terminal Remap

Docs for taking Windows terminal codes and mapping them into simple 8-bit single byte codes (for a portable editor).

//_______________________________________________/WINDOWS:KEYDOC

// _/KEYS\_____

// EN end

// ES escape

// BS backspace

// DN down

// DL delete

// HM home

// IN insert

// LF left

// PD page down

// PU page up

// RN return

// RT right

// SP space

// TB tab

// UP up

// _/EXCEPTIONS\___________________________________

// CTRL+h aliases CTRL+BACKSPACE

// CTRL+i aliases TAB

// CTRL+j aliases CTRL+RETURN

// CTRL+m aliases RETURN

// CTRL+[ aliases ESCAPE aliases control code start

// NO SHIFT+{BACKSPACE,RETURN,SPACE}

// NO CTRL+{`-=;',.z,TAB,SPACE}

// NO ALT+{TAB,RETURN}

// _/INPUT\_________________________

// =-=============-==-==-==-==-==-==

// A space........ 1b 20

// A ' ........... 1b 27

// A , ........... 1b 2c

// A - ........... 1b 2d

// A . ........... 1b 2e

// A / ........... 1b 2f

// A = ........... 1b 3d

// A 0 ........... 1b 30

// . . ........... .. ..

// A 9 ........... 1b 39

// A ; ........... 1b 3b

// A [ ........... 1b 5b

// A \ ........... 1b 5c

// A ] ........... 1b 5d

// A ` ........... 1b 60

// A a ........... 1b 61

// . . ........... .. ..

// A z ........... 1b 7a

// A backspace ... 1b 7f

// =-=============-==-==-==-==-==-==

// S tab ......... 1b 5b 5a

// =-=============-==-==-==-==-==-==

// insert ...... 1b 5b 32 7e

// delete ...... 1b 5b 33 7e

// page up ..... 1b 5b 35 7e

// page down ... 1b 5b 36 7e

// up .......... 1b 5b 41

// down ........ 1b 5b 42

// right ....... 1b 5b 43

// left ........ 1b 5b 44

// end ......... 1b 5b 46

// home ........ 1b 5b 48

// =-=============-==-==-==-==-==-==

// S insert ...... 1b 5b 32 36 32 7e

// S delete ...... 1b 5b 33 36 32 7e

// S page up ..... 1b 5b 35 36 32 7e

// S page down ... 1b 5b 36 36 32 7e

// S up .......... 1b 5b 31 3b 32 41

// S down ........ 1b 5b 31 3b 32 42

// S right ....... 1b 5b 31 3b 32 43

// S left ........ 1b 5b 31 3b 32 44

// S end ......... 1b 5b 31 3b 32 46

// S home ........ 1b 5b 31 3b 32 48

// =-=============-==-==-==-==-==-==

// C insert ...... 1b 5b 32 36 35 7e

// C delete ...... 1b 5b 33 36 35 7e

// C page up ..... 1b 5b 35 36 35 7e

// C page down ... 1b 5b 36 36 35 7e

// C up .......... 1b 5b 31 3b 35 41

// C down ........ 1b 5b 31 3b 35 42

// C right ....... 1b 5b 31 3b 35 43

// C left ........ 1b 5b 31 3b 35 44

// C end ......... 1b 5b 31 3b 35 46

// C home ........ 1b 5b 31 3b 35 48

// =-=============-==-==-==-==-==-==

// _/OUTPUT_MATCHING\_________ _/OUTPUT_CUSTOM\___________

// ==-==- ==-==- ==-==- ==-==- ==-==- ==-==- ==-==- ==-==-

// 00 20 SP 40 @ 60 ` 80 a0 SPa c0 e0 ` a

// 01 a c 21 ! 41 A 61 a 81 a1 INa c1 INc e1 a a

// 02 b c 22 " 42 B 62 b 82 a2 DLa c2 DLc e2 b a

// 03 c c 23 # 43 C 63 c 83 a3 PUa c3 PUc e3 c a

// 04 d c 24 $ 44 D 64 d 84 a4 PDa c4 PDc e4 d a

// 05 e c 25 % 45 E 65 e 85 a5 UPa c5 UPc e5 e a

// 06 f c 26 & 46 F 66 f 86 a6 DNa c6 DNc e6 f a

// 07 g c 27 ' 47 G 67 g 87 a7 RTa c7 RTc e7 g a

// 08 h c 28 ( 48 H 68 h 88 a8 LFa c8 LFc e8 h a

// 09 TB 29 ) 49 I 69 i 89 TBs a9 ENa c9 ENc e9 i a

// 0a j c 2a * 4a J 6a j 8a aa HMa ca HMc ea j a

// 0b k c 2b + 4b K 6b k 8b ab cb eb k a

// 0c l c 2c , 4c L 6c l 8c ac , a cc ec l a

// 0d RN 2d - 4d M 6d m 8d ad - a cd ed m a

// 0e n c 2e . 4e N 6e n 8e ae . a ce ee n a

// 0f o c 2f / 4f O 6f o 8f af / a cf ef o a

// 10 p c 30 0 50 P 70 p 90 b0 0 a d0 f0 p a

// 11 q c 31 1 51 Q 71 q 91 INs b1 1 a d1 IN f1 q a

// 12 r c 32 2 52 R 72 r 92 DLs b2 2 a d2 DL f2 r a

// 13 s c 33 3 53 S 73 s 93 PUs b3 3 a d3 PU f3 s a

// 14 t c 34 4 54 T 74 t 94 PDs b4 4 a d4 PD f4 t a

// 15 u c 35 5 55 U 75 u 95 UPs b5 5 a d5 UP f5 u a

// 16 v c 36 6 56 V 76 v 96 DNs b6 6 a d6 DN f6 v a

// 17 w c 37 7 57 W 77 w 97 RTs b7 7 a d7 RT f7 w a

// 18 x c 38 8 58 X 78 x 98 LFs b8 8 a d8 LF f8 x a

// 19 y c 39 9 59 Y 79 y 99 ENs b9 9 a d9 EN f9 y a

// 1a z c 3a : 5a Z 7a z 9a HMs ba da HM fa z a

// 1b ES 3b ; 5b [ 7b { 9b bb ; a db [ a fb

// 1c \ c 3c < 5c \ 7c | 9c bc dc \ a fc

// 1d ] c 3d = 5d ] 7d } 9d bd = a dd ] a fd

// 1e 3e > 5e ^ 7e ~ 9e be de fe

// 1f / c 3f ? 5f _ 7f BS 9f bf df ff BSa

// ==-==- ==-==- ==-==- ==-==- ==-==- ==-==- ==-==- ==-==-

// _/ENCODING_6_CHARS_INTO_32BIT\_________________________________

// char 0 - 7-bit

// char 1 - 7-bit

// char 2 - 0,31-5a -> 30-5a -> 0-2a -> 0-39 -> 6-bit

// char 3 - 0,36,3b,7e

// 0000000

// 0110110 ... extract 2 bits

// 0111011

// 1111110

// ab

// char 4 - 0,32,35

// 000000

// 110010 ... extract 2 bits

// 110101

// ab

// char 5 - 0,41,,7e - can just use 7-bit

// ---------------------------------------------------------------

// 11111111111111110000000000000000

// fedcba9876543210fedcba9876543210

// ================================

// .0000000........................ char 0 [lower 7-bits]

// ........1111111................. char 1 [lower 7-bits]

// ...............222222........... char 2 [clamp(c-0x30,0,0x39)]

// .....................33......... char 3 [(c>>2)&3]

// .......................44....... char 4 [(c>>1)&3]

// .........................5555555 char 5 [lower 7-bits]

________________________________________________________________________________________________________________________________

SPIR-V Notes

Aim

The point of this was to look at the possibility to replace GLSL with some simplified virtual assembly language

(something that is closer to 1:1 mapping to GCN ISA), and see if that can be expressed in SPIR-V.

I believe the answer to that is YES.

Notice that multi-component values like uvec4 get reduced to OpLoad and OpStore

without using OpPhi given a branch,

so a compiler would need to be able to handle optimizing with loads and stores.

Which implies it would be easy to just pre-allocate N*4 registers as N multi-component values,

then use load/store to access.

Tangentally, it is possible just in the examples below to see how SPIR-V is a great example of bad engineering

as SPIR-V obfuscates the meaning of code with very poor information density.

SPIR-V Reference

SPIR-V 1.0 Spec

Minimal SPIR-V File?

__GLSL__

#version 450

layout(local_size_x=64)in;

void main(){}

__SPIR-V__

; SPIR-V

; Version: 1.0

; Generator: Khronos Glslang Reference Front End; 7

; Bound: 11

; Schema: 0

OpCapability Shader

%1 = OpExtInstImport "GLSL.std.450"

OpMemoryModel Logical GLSL450

OpEntryPoint GLCompute %main "main"

OpExecutionMode %main LocalSize 64 1 1

OpSource GLSL 450

OpName %main "main"

OpDecorate %gl_WorkGroupSize BuiltIn WorkgroupSize

%void = OpTypeVoid

%3 = OpTypeFunction %void

%uint = OpTypeInt 32 0

%v3uint = OpTypeVector %uint 3

%uint_64 = OpConstant %uint 64

%uint_1 = OpConstant %uint 1

%gl_WorkGroupSize = OpConstantComposite %v3uint %uint_64 %uint_1 %uint_1

%main = OpFunction %void None %3

%5 = OpLabel

OpReturn

OpFunctionEnd

Adding Buffer Binding

__GLSL__

#version 450

layout(set=0,binding=1,std430)buffer b0_{uvec4 b0[4096];};

layout(local_size_x=64)in;

void main(){}

__SPIR-V__

; SPIR-V

; Version: 1.0

; Generator: Khronos Glslang Reference Front End; 7

; Bound: 17

; Schema: 0

OpCapability Shader

%1 = OpExtInstImport "GLSL.std.450"

OpMemoryModel Logical GLSL450

OpEntryPoint GLCompute %main "main"

OpExecutionMode %main LocalSize 64 1 1

OpSource GLSL 450

OpName %main "main"

OpName %b0_ "b0_"

OpMemberName %b0_ 0 "b0"

OpName %_ ""

OpDecorate %_arr_v4uint_uint_4096 ArrayStride 16

OpMemberDecorate %b0_ 0 Offset 0

OpDecorate %b0_ BufferBlock

OpDecorate %_ DescriptorSet 0

OpDecorate %_ Binding 1

OpDecorate %gl_WorkGroupSize BuiltIn WorkgroupSize

%void = OpTypeVoid

%3 = OpTypeFunction %void

%uint = OpTypeInt 32 0

%v4uint = OpTypeVector %uint 4

%uint_4096 = OpConstant %uint 4096

%_arr_v4uint_uint_4096 = OpTypeArray %v4uint %uint_4096

%b0_ = OpTypeStruct %_arr_v4uint_uint_4096

%_ptr_Uniform_b0_ = OpTypePointer Uniform %b0_

%_ = OpVariable %_ptr_Uniform_b0_ Uniform

%v3uint = OpTypeVector %uint 3

%uint_64 = OpConstant %uint 64

%uint_1 = OpConstant %uint 1

%gl_WorkGroupSize = OpConstantComposite %v3uint %uint_64 %uint_1 %uint_1

%main = OpFunction %void None %3

%5 = OpLabel

OpReturn

OpFunctionEnd

Buffer Load, Component Modify, Buffer Store

__GLSL__

#version 450

layout(set=0,binding=1,std430)buffer b0_{uvec4 b0[4096];};

layout(local_size_x=64)in;

void main(){uvec4 u=b0[0];u.x+=1u;b0[0]=u;}

__SPIR-V__

; SPIR-V

; Version: 1.0

; Generator: Khronos Glslang Reference Front End; 7

; Bound: 32

; Schema: 0

OpCapability Shader

%1 = OpExtInstImport "GLSL.std.450"

OpMemoryModel Logical GLSL450

OpEntryPoint GLCompute %main "main"

OpExecutionMode %main LocalSize 64 1 1

OpSource GLSL 450

OpName %main "main"

OpName %u "u"

OpName %b0_ "b0_"

OpMemberName %b0_ 0 "b0"

OpName %_ ""

OpDecorate %_arr_v4uint_uint_4096 ArrayStride 16

OpMemberDecorate %b0_ 0 Offset 0

OpDecorate %b0_ BufferBlock

OpDecorate %_ DescriptorSet 0

OpDecorate %_ Binding 1

OpDecorate %gl_WorkGroupSize BuiltIn WorkgroupSize

%void = OpTypeVoid

%3 = OpTypeFunction %void

%uint = OpTypeInt 32 0

%v4uint = OpTypeVector %uint 4

%_ptr_Function_v4uint = OpTypePointer Function %v4uint

%uint_4096 = OpConstant %uint 4096

%_arr_v4uint_uint_4096 = OpTypeArray %v4uint %uint_4096

%b0_ = OpTypeStruct %_arr_v4uint_uint_4096

%_ptr_Uniform_b0_ = OpTypePointer Uniform %b0_

%_ = OpVariable %_ptr_Uniform_b0_ Uniform

%int = OpTypeInt 32 1

%int_0 = OpConstant %int 0

%_ptr_Uniform_v4uint = OpTypePointer Uniform %v4uint

%uint_1 = OpConstant %uint 1

%uint_0 = OpConstant %uint 0

%_ptr_Function_uint = OpTypePointer Function %uint

%v3uint = OpTypeVector %uint 3

%uint_64 = OpConstant %uint 64

%gl_WorkGroupSize = OpConstantComposite %v3uint %uint_64 %uint_1 %uint_1

%main = OpFunction %void None %3

%5 = OpLabel

%u = OpVariable %_ptr_Function_v4uint Function

%18 = OpAccessChain %_ptr_Uniform_v4uint %_ %int_0 %int_0

%19 = OpLoad %v4uint %18

OpStore %u %19

%23 = OpAccessChain %_ptr_Function_uint %u %uint_0

%24 = OpLoad %uint %23

%25 = OpIAdd %uint %24 %uint_1

%26 = OpAccessChain %_ptr_Function_uint %u %uint_0

OpStore %26 %25

%27 = OpLoad %v4uint %u

%28 = OpAccessChain %_ptr_Uniform_v4uint %_ %int_0 %int_0

OpStore %28 %27

OpReturn

OpFunctionEnd

Now With Simple Conditional

__GLSL__

#version 450

layout(set=0,binding=1,std430)buffer b0_{uvec4 b0[4096];};

layout(local_size_x=64)in;

void main(){uvec4 u=b0[0];if(u.x!=0u)u.x+=1u;else u.x+=2u;b0[0]=u;}

__SPIR-V__

; SPIR-V

; Version: 1.0

; Generator: Khronos Glslang Reference Front End; 7

; Bound: 44

; Schema: 0

OpCapability Shader

%1 = OpExtInstImport "GLSL.std.450"

OpMemoryModel Logical GLSL450

OpEntryPoint GLCompute %main "main"

OpExecutionMode %main LocalSize 64 1 1

OpSource GLSL 450

OpName %main "main"

OpName %u "u"

OpName %b0_ "b0_"

OpMemberName %b0_ 0 "b0"

OpName %_ ""

OpDecorate %_arr_v4uint_uint_4096 ArrayStride 16

OpMemberDecorate %b0_ 0 Offset 0

OpDecorate %b0_ BufferBlock

OpDecorate %_ DescriptorSet 0

OpDecorate %_ Binding 1

OpDecorate %gl_WorkGroupSize BuiltIn WorkgroupSize

%void = OpTypeVoid

%3 = OpTypeFunction %void

%uint = OpTypeInt 32 0

%v4uint = OpTypeVector %uint 4

%_ptr_Function_v4uint = OpTypePointer Function %v4uint

%uint_4096 = OpConstant %uint 4096

%_arr_v4uint_uint_4096 = OpTypeArray %v4uint %uint_4096

%b0_ = OpTypeStruct %_arr_v4uint_uint_4096

%_ptr_Uniform_b0_ = OpTypePointer Uniform %b0_

%_ = OpVariable %_ptr_Uniform_b0_ Uniform

%int = OpTypeInt 32 1

%int_0 = OpConstant %int 0

%_ptr_Uniform_v4uint = OpTypePointer Uniform %v4uint

%uint_0 = OpConstant %uint 0

%_ptr_Function_uint = OpTypePointer Function %uint

%bool = OpTypeBool

%uint_1 = OpConstant %uint 1

%uint_2 = OpConstant %uint 2

%v3uint = OpTypeVector %uint 3

%uint_64 = OpConstant %uint 64

%gl_WorkGroupSize = OpConstantComposite %v3uint %uint_64 %uint_1 %uint_1

%main = OpFunction %void None %3

%5 = OpLabel

%u = OpVariable %_ptr_Function_v4uint Function

%18 = OpAccessChain %_ptr_Uniform_v4uint %_ %int_0 %int_0

%19 = OpLoad %v4uint %18

OpStore %u %19

%22 = OpAccessChain %_ptr_Function_uint %u %uint_0

%23 = OpLoad %uint %22

%25 = OpINotEqual %bool %23 %uint_0

OpSelectionMerge %27 None

OpBranchConditional %25 %26 %33

%26 = OpLabel

%29 = OpAccessChain %_ptr_Function_uint %u %uint_0

%30 = OpLoad %uint %29

%31 = OpIAdd %uint %30 %uint_1

%32 = OpAccessChain %_ptr_Function_uint %u %uint_0

OpStore %32 %31

OpBranch %27

%33 = OpLabel

%35 = OpAccessChain %_ptr_Function_uint %u %uint_0

%36 = OpLoad %uint %35

%37 = OpIAdd %uint %36 %uint_2

%38 = OpAccessChain %_ptr_Function_uint %u %uint_0

OpStore %38 %37

OpBranch %27

%27 = OpLabel

%39 = OpLoad %v4uint %u

%40 = OpAccessChain %_ptr_Uniform_v4uint %_ %int_0 %int_0

OpStore %40 %39

OpReturn

OpFunctionEnd

________________________________________________________________________________________________________________________________

Shipping Only 16-Bit

TLDR, going to require 16-bit shader support!

One man show, avoiding having both a 32-bit and 16-bit shader variation is highly desired.

Don't want to limit the tech based on decisions required to support 32-bit.

Would it be practical to develop and ship just a 16-bit version?

This is Vulkan only, no XBox (for certain), and no Playstation (lack of time).

Don't need 16-bit buffer access, and wave size is managed via spec constants, so relatively easy.

vulkan.gpuinfo.org - VkPhysicalDeviceFeatures::shaderInt16 - VK_KHR_shader_float16_int8::shaderFloat16

- AMD : GCN5 (Vega) and up. Hits Steam Deck (assuming they have 16-bit support in the software stack, RADV does apparently).

Note GCN4 (Polaris) has single rate 16-bit so that would be supported if AMD would stop disabling it in software.

- Intel : This says 16-bit support since Gen8 (at least in Linux).

Beyond Arc, not sure if Intel iGPUs will be fast enough to run this project.

Assuming Gen11 baseline maybe, and would need to also have 16-wide wave permutation to be optimal.

- NVIDIA : Turing (aka 20 series) and up. NV lacks some of the ISA support, but likely its emulated.

NVIDIA is not a performance limited target, so will take 'no perf uplift' or even a 'slight reduction in perf' to avoid authoring a 32-bit only shader variations.

Adding up the top cards (all NVIDIA) on

Steam Hardware Survey

shows at least 30% market won't support 16-bit.

But also that at least 30% of the market will support 16-bit, and that is good enough for me.

________________________________________________________________________________________________________________________________

X68 Epilogue

Keeping notes here incase I ever choose to revisit ...

The time for this project was replaced by [SBC].

The ability to write GPU binaries and command buffers was too great,

and after that there is effectively no need for any CPU logic except the ugly that is interfacing inside a modern OS.

________________________________

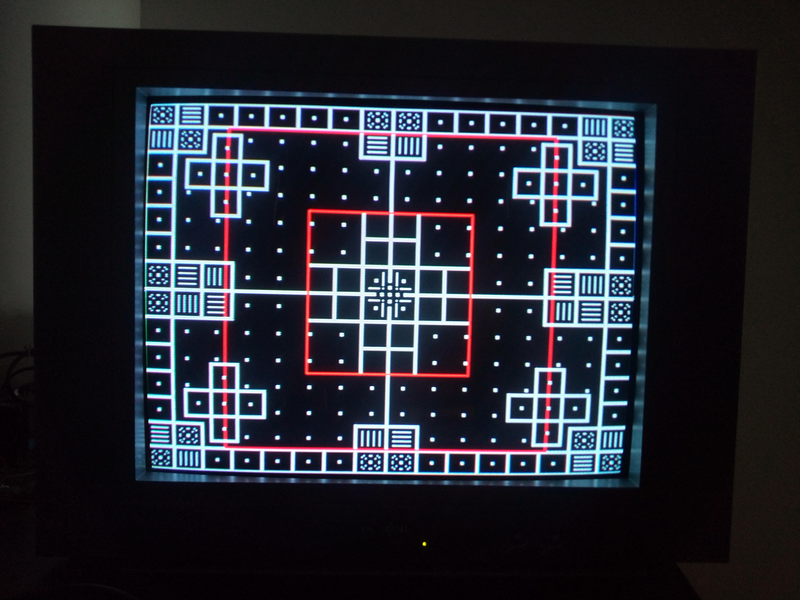

[PR0] Random Prototype 0

TODO, out of time perhaps more on these later...

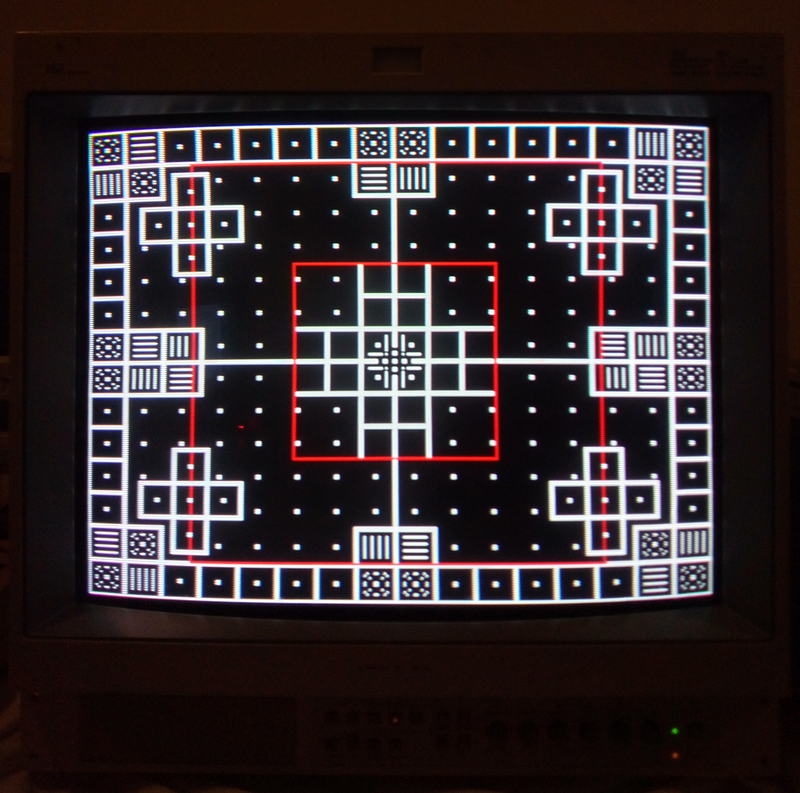

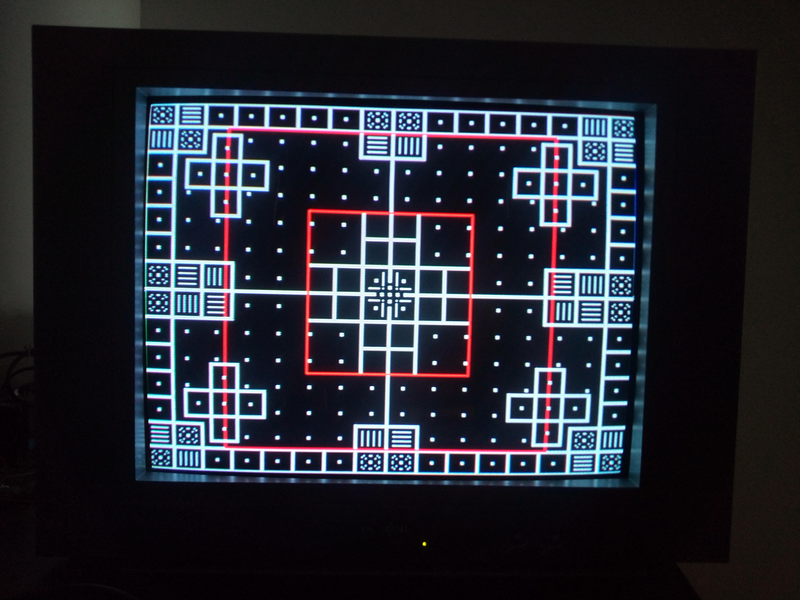

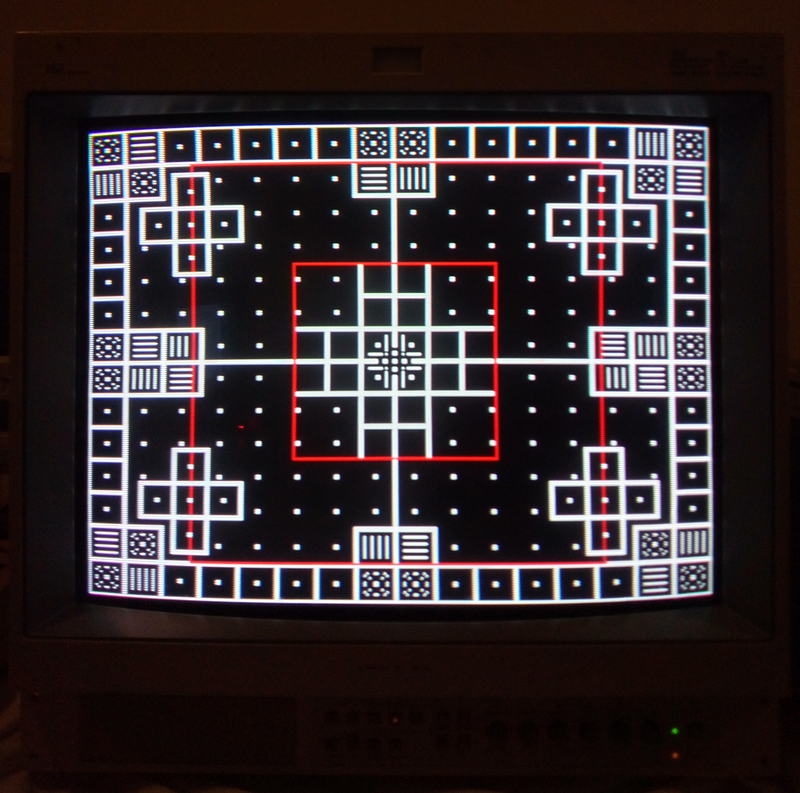

Raw View Without Hole Filling Or Temporal Reconstruction

Majority of white dots are actually holes in the scene.

This is using stratified visibility, it doesn't necessarily find an intersection for each pixel.

With Temporal Reconstruction and Grain

This uses a spatial temporal reconstruction that also fills holes and removes noise.

________________________________________________________________________________________________________________________________

[PR0] Octahedral Framebuffer

Implemnted a 1024x512 rectangular layout octahedral framebuffer,

with a 360 degree cylindrical projection in a three stage pipeline.

The intermediate stage samples the octahedron

into a VGA-like 720x256 resolution target with a warped vertical.

This is to avoid perspective induced undersampling.

Final stage applies the CRT shader.

CRT shader has progressively thicker scanlines at top and bottom due to the vertical warpage.

Running full 16:9 but with a strong vignette.

The shadow mask is blended out towards the center of the screen to increase peak brightness

Horizontal blur is increased towards the right and left for the chromatic aberration.

Both the sampling of the octahedron and the VGA intermediate images are done with linear filtering

and a wide gaussian kernel.

Monochromatic tonemapping is applied afterwards.

Followed by linear-space colorizing of the greyscale.

The octahedron output is 32-bit packed {8-bit 1/(1+luma) in gamma 2.0, 13-bit x, 11-bit y}.

Sub-pixel position will later be used in filtering.

Shots below have linear temporal average of simple ray traced dummy scene,

enough to show first pass of post pipeline.

Have some changes to try before moving on to the next step in development.

Not planning on doing bloom, due to the wide gaussian kernel bright areas naturally have a slight bleed,

that is likely enough hint of brightness.

Not going to do DOF, following the strategy, if it cannot be done really well, don't bother.

Not doing motion blur, as there are no hard edges for the eye to get stuck on,

focusing on peak frame rate instead.

Not doing local contrast adaption or sharpening of any kind,

don't like the look of negative lobes inverting the edge.

________________________________________________________________________________________________________________________________

[PR0] GPU Program Bring Up

Not yet to the fun part, still laying down foundation.

Added a frame counter as a push constant for the single dispatch.

This will be enough to branch on to get to even and odd frame permutations.

So that double buffering works properly.

Dispatch sizing is a fixed 2K workgroups.

Which in theory at 64 VGPRs/wave target, is good for a 128 CU machine (in classic GCN arch).

Classic GCN has maxed out at a 64 CU machine.

Will have to modify this stuff later.

Bringing up helper GLSL structure, binding points, etc.

Initial testing involved writing to the front buffer a color based on the frame count push constant.

Front buffer rendering seems to "work" both when full-screen (low latency) and windowed (high latency).

Example screen shot shows {red,black} color due to window compositor reading during program writes.

Software Spin Wait -

With pipelined execution, a wait on a "barrier" would be expected to not wait.

The barrier only functions as a safe-guard in case something goes wrong.

Initial check to see if a barrier is signaled should thus involve a cached read

(because there would be an expectation of other waves later reading the same value).

Only if the initial read fails should an uncached spin wait be invoked.

Can see from the RDNA ISA Guide,

hardware support both in scalar and vector loads for GLC=0 reads which hit on the cache,

and GLC=1 reads which force a fetch from L2, and evict the line afterwards ("miss-evict").

Ideal spin wait would be the following,

// Want this logic in SALU only (no burning vector ALU cycles).

if(ramR.barrier<signal){ // (A.) SMEM GLC=0 read, only enter if not signaled.

while(ramRV.barrier<signal){}} // (B.) SMEM GLC=1 read, spin while not signaled.

The first wave would miss on the first (A.) read.

If the barrier passes, all future waves will hit and quickly pass.

If the spin (B.) is invoked, the second wave will miss on the first (A.) read,

because GLC=1 evicts the line post-read.

But the third will hit.

API ASK #0 - Ability to provide branch hints (coherent vs divergent, and expected branch outcome).

The compiler output (see below) is always the slower option.

It keeps the most uncommon path inline resulting in the most inefficient execution.

HARDWARE ASK #0 - Would be nice to have a way to force a miss on read but leave the line in the cache.

AMD DRIVER BUG #0 -

AMD driver sees "readonly" then ignores the other memory qualifiers.

This is both a correctness and optimization bug.

So there is no way to get SMEM loads with GLC=1 set.

This pushes the overhead into the VMEM and VALU paths for (B.).

If the first wave sees a non-signaled state in (A.)

then likely all waves on that cache will always invoke the slower (B.) spin loop,

because nothing will be refreshing the K$ line.

// layout(set=0,binding=2,std430)readonly buffer ssbo3_ {RamT ramRV;};

s_buffer_load_dword s0, s[12:15], null // 000000000020: F4200006 FA000000

// layout(set=0,binding=2,std430)volatile readonly buffer ssbo3_ {RamT ramRV;};

s_buffer_load_dword s0, s[12:15], null // 000000000020: F4200006 FA000000

// layout(set=0,binding=2,std430)coherent readonly buffer ssbo3_ {RamT ramV;};

s_buffer_load_dword s0, s[12:15], null // 000000000020: F4200006 FA000000

// layout(set=0,binding=2,std430)volatile buffer ssbo3_ {RamT ramRV;};

buffer_load_dword v1, v0, s[12:15], 0 dlc glc // 000000000020: E030C000 80030100

// layout(set=0,binding=2,std430)coherent buffer ssbo3_ {RamT ramRV;};

buffer_load_dword v1, v0, s[12:15], 0 dlc glc // 000000000020: E030C000 80030100

AMD DRIVER BUG #1 -

The above code with the VMEM spin workaround won't work due to this second bug.

AMD driver incorrectly hoists the VMEM GLC=1 load outside the loop, leading to incorrect behavior.

In the example below the signal state is zero (instead of less than some number).

if(ramR.barrier!=0u){ // (A.).

while(ramV.barrier!=0u){}} // (B.).

// This is (A.).

s_buffer_load_dword s0, s[12:15], null // 000000000028: F4200006 FA000000

s_waitcnt lgkmcnt(0) // 000000000030: BF8CC07F

s_cmp_eq_i32 s0, 0 // 000000000034: BF008000

s_cbranch_scc1 label_006C // 000000000038: BF85000C

// This should be in the (B.) loop.

buffer_load_dword v1, v0, s[12:15], 0 dlc glc // 00000000003C: E030C000 80030100

s_nop 0x0000 // 000000000044: BF800000

s_nop 0x0000 // 000000000048: BF800000

s_nop 0x0000 // 00000000004C: BF800000

s_nop 0x0000 // 000000000050: BF800000

s_nop 0x0000 // 000000000054: BF800000

s_nop 0x0000 // 000000000058: BF800000

s_nop 0x0000 // 00000000005C: BF800000

// This is (B.).

label_0060:

s_waitcnt vmcnt(0) // 000000000060: BF8C3F70

v_cmp_eq_i32 vcc_lo, 0, v1 // 000000000064: 7D040280

s_cbranch_vccz label_0060 // 000000000068: BF86FFFD

label_006C:

AMD DRIVER BUG #2 -

Now trying to trick the compiler into doing the right thing.

First with 'subgroupElect()', which generates the same bug as prior,

but adds another performance bug.

This should just be a simple operation to save and set EXEC to 1, then restore afterwards.

But instead the compiler acts as if it is already in divergent control flow ('ff1' is find first 1).

if(subgroupElect()){if(ramR.barrier!=0u){while(ramV.barrier!=0u){}}}

// This is the subgroupElect() code for a wave sized workgroup in known coherent execution.

v_mbcnt_lo_u32_b32 v1, -1, 0 // 000000000010: D7650001 000100C1

s_ff1_i32_b64 s0, exec // 000000000018: BE80147E

v_mbcnt_hi_u32_b32 v1, -1, v1 // 00000000001C: D7660001 000202C1

. . .

s_and_saveexec_b64 s[10:11], vcc // 000000000028: BE8A246A

AMD DRIVER BUG #3 -

Trying to work around the above performance bug (since running work for just lane 0 will be needed elsewhere).

Using 'gl_LocalInvocationID.x' paired with 'layout(local_size_x=32)' won't work either.

This example gets 'wave_size(32)' in the disassembly.

The compiler still uses VALU work instead of just masking EXEC.

if(gl_LocalInvocationID.x==0u){if(ramR.barrier!=0u){while(ramV.barrier!=0u){}}}

v_cmp_eq_i32 vcc_lo, 0, v0 // 000000000010: 7D040080

s_and_saveexec_b32 s0, vcc_lo // 000000000014: BE803C6A

s_cbranch_execz label_006C // 000000000018: BF880014

AMD DRIVER BUG #4 -

Last attempt to workaround the performance bug also fails.

The driver will always use the slow path burning VALU instruction(s)

for what should map to one 'S_AND_SAVEEXEC_B32 s[...],1' scalar instruction on Navi.

Using subgroup ops results in 'wave_size(64)' in the disassembly.

if(gl_SubgroupInvocationID==0u){if(ramR.barrier!=0u){while(ramV.barrier!=0u){}}}

v_mbcnt_lo_u32_b32 v1, -1, 0 // 000000000010: D7650001 000100C1

v_mbcnt_hi_u32_b32 v1, -1, v1 // 000000000018: D7660001 000202C1

v_cmp_gt_i32 vcc, 1, v1 // 000000000020: 7D080281

s_and_saveexec_b64 s[10:11], vcc // 000000000024: BE8A246A

AMD DRIVER BUG #5 -

There is another obvious bug in the above disassembly.

The program is using 'layout(local_size_x=32)'

and using 'gl_SubgroupInvocationID' or 'subgroupElect()' causes the compiler to switch to 'wave_size(64)' mode

with the high 32 lanes doing nothing.

This also means it is using 'V_MBCNT_HI_U32_B32' which wouldn't be needed in wave32 mode.

AMD DRIVER BUG #6 -

Using 'VK_EXT_subgroup_size_control' doesn't support forcing wave32 mode on Navi.

Takeaways?

If software prevents you from accessing it, the hardware doesn't actually exist.

All reasonable efforts to optimize on AMD are thwarted by it's software stack.

No choice but to ship with the slowest path on the hardware.

One optimization is possible however,

early in execution, going to process 'gl_LocalInvocationID' to write a waveID into an SGPR.

This way the VGPR for 'gl_LocalInvocationID' can be freed.

Later will use 'gl_SubgroupInvocationID' when required to build a lane index

(which materializes lane index from ALU instead of keeping it in a VGPR).

________________________________________________________________________________________________________________________________

[PR0] ABI Crossing

Thoughts on interfacing a custom language to library calls, didn't end up using the custom language for this project...

Stack Crossing

System ABIs use 16-byte aligned stacks.

ABI REQUIREMENTS AFTER A CALL INSTRUCTION

=========================================

[rsp+8] SYSV 7th argument, WIN first entry of 32-byte shadow space

[rsp+0] Return address, this is 16-byte aligned

[rsp-8] Free space

RSP BEFORE A CALL IS THUS NOT 16-BYTE ALIGNED

=============================================

[rsp+0] SYSV 7th argument, WIN first entry of 32-byte shadow space

This will use 8-byte aligned stacks, because they are not used for 16-byte data.

The ABI crossing call will need to start by aligning the stack, and restoring it before the return.

// Aligned case,

// [64] [rsp ] return address

// [56] [rsp-8 ] save rsp ....... skipped

// [48] [rsp-16] save rsp ....... final rsp points here

// -----------------------------------------------------

// Unaligned case,

// [56] [rsp ] return address

// [48] [rsp-8 ] save rsp ....... final rsp points here

// [40] [rsp-16] save rsp ....... unused

// -----------------------------------------------------

enter:

mov [rsp-8],rsp

mov [rsp-16],rsp

add rsp,-8

and rsp,~15

...

leave:

mov rsp,[rsp+0]

ret

ABIs

Only supporting x86-64 in 64-bit mode for this project.

Have a few points to cross between my custom non-language and the rest of the system.

C ABI different for Windows vs everyone else, and system calls on non-windows platforms.

The 'a' is an argument (numbered), the 'non' is non-volatile, 'vol' is volatile, and everything else is volatile.

The 'WIN' is the Windows ABI, the 'SYSV' is shared across unix/BSDs, the 'KRN' is the Linux kernel syscall convention.

REG X86-FAIL WIN SYSV KRN

======== ======== ====== ====== =======

r0 (rax) ........ return return num/ret --- reuse for call address or syscall number

r1 (rcx) ........ a0 ... a3 ... vol ... --- save

r2 (rdx) ........ a1 ... a2 ... a2 .... --- save

r3 (rbx) ........ non .. non .. non ...

r4 (rsp) SIB .... stack stack stack . --- save

r5 (rbp) RIP .... non .. non .. non ...

r6 (rsi) ........ non .. a1 ... a1 .... --- save on non-win

r7 (rdi) ........ non .. a0 ... a0 .... --- save on non-win

r8 ..... ........ a2 ... a4 ... a4 .... --- save

r9 ..... ........ a3 ... a5 ... a5 .... --- save

r10 .... ........ vol .. vol .. a3 .... --- save

r11 .... ........ vol .. vol .. vol ... --- save

r12 .... SIB .... non .. non .. non ...

r13 .... RIP .... non .. non .. non ...

r14 .... ........ non .. non .. non ...

r15 .... ........ non .. non .. non ...

Stacks must be 16-byte aligned, showing state of the stack after a call.

WIN STACK CONVENTION

====================

| [rsp+0x80] a16

[rsp+0x78] a15

| [rsp+0x70] a14

[rsp+0x68] a13

| [rsp+0x60] a12

[rsp+0x58] a11

| [rsp+0x50] a10

[rsp+0x48] a9

| [rsp+0x40] a8

[rsp+0x38] a7

| [rsp+0x30] a6

[rsp+0x28] a5

| [rsp+0x20] Shadow space

[rsp+0x18] Shadow space

| [rsp+0x10] Shadow space

[rsp+0x08] Shadow space

| [rsp+0x00] Return address, must be 16-byte aligned (rsp after call)

SYSV STACK CONVENTION

=====================

| [rsp+0x50] a16

[rsp+0x48] a15

| [rsp+0x40] a14

[rsp+0x38] a13

| [rsp+0x30] a12

[rsp+0x28] a11

| [rsp+0x20] a10

[rsp+0x18] a9

| [rsp+0x10] a8

[rsp+0x08] a7

| [rsp+0x00] Return address, must be 16-byte aligned (rsp after call)

Expected language crossing granularity is low,

so I'm not inclined to do anything other than make it easy to manage.

A language crossing will include a stack crossing as well,

as I'm not going to keep rsp 16-byte aligned.

This is bloody ugly, but it will work.

Will have to check if I have any language crossings using floating point.

ENGINE CONVENTION

=================

| [rsp+0xb8] r11

[rsp+0xb0] r10

| [rsp+0xa8] r9

[rsp+0xa0] r8

| [rsp+0x98] rdx

[rsp+0x90] rsi

| [rsp+0x88] rsp

[rsp+0x80] rdx (save volatile)

----------------

| [rsp+0x78] a16 (args)

[rsp+0x70] a15

| [rsp+0x68] a14

[rsp+0x60] a13

| [rsp+0x58] a12

[rsp+0x50] a11

| [rsp+0x48] a10

[rsp+0x40] a9

| [rsp+0x38] a8

[rsp+0x30] a7 (adjusted pointer sysv only)

| [rsp+0x28] a6 (register copy sysv only)

[rsp+0x20] a5 (register copy sysv only)

| [rsp+0x18] a4 (copied back to registers before the call)

[rsp+0x10] a3

| [rsp+0x08] a2

[rsp+0x00] a1

// On entry,

// - rax is the address to call

// - rcx is future stack pointer for call

entry:

mov [rcx+0x80],rdx

mov [rcx+0x88],rsp

#if SYSV

mov [rcx+0x90],rsi

mov [rcx+0x98],rdi

#endif

mov [rcx+0xa0],r8

mov [rcx+0xa8],r9

mov [rcx+0xb0],r10

mov [rcx+0xb8],r11

#if WIN

mov rsp,rcx

mov r9,[rcx+0x18]

mov r8,[rcx+0x10]

mov rdx,[rcx+0x08]

mov rcx,[rcx+0x00]

#endif

#if SYSV

lea rsp,[rcx+0x30]

mov r8,[rcx+0x20]

mov r9,[rcx+0x28]

mov rdi,[rcx+0x00]

mov rsi,[rcx+0x08]

mov rdx,[rcx+0x10]

mov rcx,[rcx+0x18]

#endif

call rax

#if WIN

mov rdx,[rsp+0x80]

mov r8,[rsp+0xa0]

mov r9,[rsp+0xa8]

mov r10,[rsp+0xb0]

mov r11,[rsp+0xb8]

mov rsp,[rsp+0x88]

#endif

#if SYSV

mov rdx,[rsp+0x80-0x30]

mov rsi,[rcx+0x90-0x30]

mov rdi,[rcx+0x98-0x30]

mov r8,[rcx+0xa0-0x30]

mov r9,[rcx+0xa8-0x30]

mov r10,[rcx+0xb0-0x30]

mov r11,[rcx+0xb8-0x30]

mov rsp,[rcx+0x88-0x30]

#endif

ret

________________________________

[GPU] Links

________________________________________________________________________________________________________________________________

[GPU] 3D Barycentric

Useful for skinning volumetric data

d=1-(a+b+c) ... coordinates must sum to one

r = point to convert into barycentric

r{a,b,c,d} = points of tetrahedron

{a,b,c} = inv(T)*(r-rd)

T =

x1-x4 x2-x4 x3-x4

y1-y4 y2-y4 y3-y4

z1-z4 z2-z4 z3-z4

INVERT A 3x3 MATRIX

=======================

a b c

d e f = A

g h i

(ei-fh) -(bi-ch) (bf-ce)

-(di-fg) (ai-cg) -(af-cd) * 1/det(A)

(dh-eg) -(ah-bg) (ae-bd)

det(A)

(ei-fh) * a -(di-fg) * b + (dh-eg) * c

________________________________________________________________________________________________________________________________

[GPU] Shader Device Clock

VK_KHR_shader_clock - device clock support

- AMD/NVIDIA : Supports device clock on all platforms that have 16-bit support

- Intel : No support for shader device clock

TODO: Is NVIDIA's device shader clock a consistent frequency?

________________________________________________________________________________________________________________________________

[GPU] Wave OPs

Suggestion of API and implementation for wave operations.

This is a copy of what I like for personal development.

=========

TERMS

=========

P1 ... 'predicate' (bool single component)

I1 ... 'integer' (32-bit signed integer single component)

UI1 .. 'unsigned integer'

W1 ... 'word' (16-bit signed integer)

C .... 'coherent' (function is static or dynamically uniform control flow)

V .... 'volatile' (function can be called in unknown control flow)

=====================================

AVOIDING PROBLEMS WITH DIVERGENCE

=====================================

Pass around 'P1 laneMask' and only go into divergent control flow locally.

This requires a different style of programming.

P1 laneMask = ...; // Existing lane mask value.

P1 laneMask2 = laneMask & newMask; // Make a local lane mask for a new subset of active threads.

if(laneMask2){ ... } // Do logic which is limited to a subset of lanes.

f(laneMask,...); // Do logic which is limited to older subset of lanes.

Note above, 'f()' gets the lane mask passed in.

So 'f()' is always called from dynamically uniform control flow.

And can thus do any operations that require all lanes active.

The standard method of possibly having dynamically divergent control flow cannot do that.

=======

API

=======

NO 'gl_SubgroupInvocationID' or 'WaveGetLaneIndex()'

- INSTEAD only launch 1D workgroups and compute from 'gl_LocalInvocationID.x' and 'SV_GroupThreadID.x'

- 2D coordiates are always generated from a 1D workgroup due to needing lane swizzling to get perf

- Shader can avoid the AND operation if workgroup is know to be wave sized

- May want to maintain a 16-bit lane index to save space in some cases

- AMD

- The 'gl_LocalInvocationID.x' is placed in 'v0' before program launch (fast path)

- Driver will NOT optimize 'gl_SubgroupInvocationID' to 'gl_LocalInvocationID.x'

- The 'gl_SubgroupInvocationID' gets built (slow path)

- Using 2 VALU instructions via V_MBCNT_{HI,LO}_U32_B32 which is possibly slower (wave64, or 1 op wave32)

NO GENERIC SHUFFLE VIA 'subgroupShuffle()' OR 'WaveReadLaneAt(,nonUniformValue)'

- This is because of min spec hardware portability

- See 'Quad' and 'WaveXor' cases for constrained shuffle usage

- AMD

- DS_SWIZZLE_B32 only works in groups of 32 lanes (on GCN and RDNA)

- Same with the introduction of DS_*PERMUTE_B32 (note AMD ISA guide has some incorrect descriptions on this)

- GCN hardware is only wave64

- No way to easily portably force wave32 on RDNA

- So no way to guarantee usage of DS_BPERMUTE_B32 (wave32 only path)

- The wave64 path ends up using a V_READLANE_B32 waterfall loop (could be 64 interations, so unusably slow)

- Forced to use LDS for this kind of functionality

- No need for new API to use LDS

NO USING 'subgroupElect()' OR 'WaveIsFirstLane()'

- Both have the overhead of needing to find the first lane in possibly divergent control flow

- They are thus slow

- Instead manually mask to lane 0 via 'if((gl_LocalInvocationID.x & waveSizeMinusOne)==0)'

- Where the AND part is skipped for wave sized workgroups

- AMD

- Driver output for 'subgroupElect()' is expensive

- It is not optimized for even compile-time known uniform control flow

NO READ-FIRST-LANE

- Because on some platforms this implies using 'find-first-one' to figure out the first active lane

- So instead only call from non-divergent control flow and use explicit lane=0 in function calls

- This will be slightly less optimal (probably not measurable) on AMD, but better overall

- AMD

- 'V_READFIRSTLANE_B32 d,s' is a 32-bit instruction

- 'V_READLANE_B32 d,s,0' is a 64-bit instruction (slightly less optimal)

WITH SOME EXCEPTIONS, NO LANE SHARING BEYOND GROUPS OF 16 LANES

- Supported on all AMD and NVIDIA hardware

- Should in theory work on Intel hardware (they can do wave16)

- Wave16 is their fast path

- Exceptions

- Single lane read/write

- Ballot

I1 Quad{0,1,2,3,X,Y,D}CI1(I1 v)

- {0,1,2,3} selects quad element

- Separate functions force compile-time uniformity (portable fast path)

- DX: QuadReadLaneAt(,{0,1,2,3})

- VK: subgroupQuadBroadcast(,{0,1,2,3})

- {X,Y,D} swap with directional neighbor

- DX: QuadReadAcross{X,Y,Diagonal}()

- VK: subgroupQuadSwap{Horizontal,Vertical,Diagonal}()

- AMD: all DPP ops (fast path)

- GL: emulation?

- Can use dFd{x,y}Fine() functions for emulation

- See 'GPU Pro 2' "Shader Amortization using Pixel Quad Message Passing"

- However {ES,WebGL} lacks the 'Fine()' functions

- ES?: might be able to use 'GL_FRAGMENT_SHADER_DERIVATIVE_HINT' 'GL_NICEST'

void WavePutCI1(inout I1 dst, I1 src, I1 dynamicallyUniformLaneDst, I1 laneSrc)

- Emulation is possible because 'C' (only callable from dynamically uniform flow control)

- This could be useful for storing stacks in a VGPR

- This is a function since it can be mapped without emulation to a hardware instruction on AMD

- The 'laneSrc' is passed in to enable fast path if wave-sized workgroups vs multi-wave workgroups

- Usage,

WavePutCI1(dst, src, 2, (gl_LocalInvocationID.x & waveSizeMinusOne))

WavePutCI1(dst, src, 2, gl_LocalInvocationID.x )

- Emulation,

if(dynamicallyUniformLaneDst == laneSrc) d = x;

- AMD: V_WRITELANE_B32

- Ignores EXEC mask

I1 WaveGetCI1(I1 src, I1 dynamicallyUniformLaneSrc)

- Return 'src' value from lane 'dynamicallyUniformLaneSrc'

- For review the 'C' is 'coherent' meaning can only be called from dynamically uniform control flow

- For review the 'I1' is 32-bit integer

- AMD: V_READLANE_B32

- Works for wave32|wave64

- Ignores EXEC mask

I1 WaveXor1CI1(I1 src)

I1 WaveXor2CI1(I1 src)

I1 WaveXor4CI1(I1 src)

I1 WaveXor8CI1(I1 src)

- Designed to support 2D reductions from 4x4:1

- Requires minimum wave16 support (Intel's fast path)

- VK: subgroupShuffleXor(src, {1,2,4,8})

- DX

- AMD

- subgroupShuffleXor(,{1,2}) uses DPP quad permute

- subgroupShuffleXor(,4) uses DPP row XOR mask

- subgroupShuffleXor(,8) uses DPP row rotate by 8

- subgroupShuffleXor(,16) uses DS_SWIZZLE_B32 (which requires S_WAITCNT, slower)

- subgroupShuffleXor(,32) uses a horrible amount of code for wave64 (unusably slow)

FOR REFERENCE, THE CORRECT WAY TO DO ATOMIC APPEND

- This gets around stupid driver behavior of AMD

- AMD pattern matches atomicAdd(,staticUniform) and turns it into garbage

- Can fix it by atomicAdd(,dynamicallyUniform) where the compiler doesn't see staticUniform

- Instead do this,

P1 p=...; // Set to true to append, false to not append

UI4 b=subgroupBallot(p);

UI1 stopStupid=gl_LocalInvocationID.x>>31; // Generate a VGPR zero that the compiler doesn't pattern match

UI1 c=subgroupBallotBitCount(b)+stopStupid; // Force the compiler to promote from SGPR to VGPR

UI1 d=0;

if(gl_LocalInvocationID.x==0)d=atomicAdd(...,c); // Do the atomic on lane zero only

UI1 e=subgroupBallotExclusiveBitCount(b); // Factor this work in the latency window of the atomic add

subgroupBarrier(); // Required to be API safe

d=subgroupBroadcast(d,0); // Fast lane zero broadcast avoids 'find-first-one' overhead

d+=e; // Output position for append

________________________________________________________________________________________________________________________________

[GPU] Float Bool Fixes

There are times when there is a need to do bool logic inside floating point numbers.

Here is a good starting point for implementing such logic,

with comments about implementation on AMD GPUs.

- 1.0 ............ true

- 0.0 ............ false

- And(x,y) ....... min(x,y)

- And(x,y) ....... saturate(x*y)

- And3(x,y,z) .... min3(x,y,z) ........ 1 op (32-bit/16-bit), 2 ops (packed 16-bit, no packed MIN3)

- AndOr(x,y,z) ... saturate(x*y+z)

- AndNot(x,y) .... -x*y+1.0

- Gt(x,y) ........ Gtz(x-y) ........... 2 ops

- Gtz(x) ......... saturate( INF*x) ... {NaN := 0, x GT 0 := 1, else 0}

- Lt(x,y) ........ Ltz(x-y) ........... 2 ops

- Ltz(x) ......... saturate(-INF*x) ... {NaN := 0, x LT 0 := 1, else 0}

- Ne(x,y) ........ Gtz(abs(x-y)) ...... 2 ops (32-bit), 3 ops (16-bit, ABS not free)

- Not(x) ......... 1.0-x

- Or(x,y) ........ max(x,y)

- Or(x,y) ........ saturate(x+y)

- Or3(x,y,z) ..... max3(x,y,z) ........ 1 op (32-bit/16-bit), 2 ops (packed 16-bit, no packedk MAX3)

- Sel(x,y,z) ..... z*y+((-z)*x+x) ..... z==0.0?x:y, 2 ops, preserves precision

The following get more expensive (extra op).

- Le(x,y) ... Not(Gt(x,y))

- Ge(x,y) ... Not(Lt(x,y))

- Eq(x,y) ... Not(Ne(x,y))

They could be faster if there was a way to run the hardware in a mode without NaNs,

with modified floating point rules.

- INF-INF := NaN ...... Actual IEEE rule (a problem)

- (+/-)INF*0 := NaN ... Actual IEEE rule (a problem)

- WOULD RATHER HAVE NO NANs AND INSTEAD THIS LOGIC

- -INF+INF := 0 ....... Desired rule

- -INF-INF := -INF .... Desired rule

- +INF+INF := +INF .... Desired rule

- SO THE FOLLOWING IS POSSIBLE

- Eq(x,y) ............. saturate(-INF*abs(x-y)+INF)

- Ge(x,y) ............. Gez(x-y)

- Gez(x) .............. saturate(+INF*x+INF)

- Le(x,y) ............. Lez(x-y)

- Lez(x) .............. saturate(-INF*x+INF)

Detailed logic using new rules.

EQ

==

saturate((-INF*{ 0.0})+INF) ... saturate(( 0.0)+INF) ... saturate(+INF) ... 1.0

saturate((-INF*{+INF})+INF) ... saturate((-INF)+INF) ... saturate( 0.0) ... 0.0

saturate((-INF*{ +})+INF) ... saturate((-INF)+INF) ... saturate( 0.0) ... 0.0

GEZ

===

saturate((+INF*{ 0.0})+INF) ... saturate(( 0.0)+INF) ... saturate(+INF) ... 1.0

saturate((+INF*{-INF})+INF) ... saturate((-INF)+INF) ... saturate( 0.0) ... 0.0

saturate((+INF*{ -})+INF) ... saturate((-INF)+INF) ... saturate( 0.0) ... 0.0

saturate((+INF*{+INF})+INF) ... saturate((+INF)+INF) ... saturate(+INF) ... 1.0

saturate((+INF*{ +})+INF) ... saturate((+INF)+INF) ... saturate(+INF) ... 1.0

LEZ

===

saturate((-INF*{ 0.0})+INF) ... saturate(( 0.0)+INF) ... saturate(+INF) ... 1.0

saturate((-INF*{-INF})+INF) ... saturate((+INF)+INF) ... saturate(+INF) ... 1.0

saturate((-INF*{ -})+INF) ... saturate((+INF)+INF) ... saturate(+INF) ... 1.0

saturate((-INF*{+INF})+INF) ... saturate((-INF)+INF) ... saturate( 0.0) ... 0.0

saturate((-INF*{ +})+INF) ... saturate((-INF)+INF) ... saturate( 0.0) ... 0.0

Case For Hardware FAMA

- Leverage all of the typical register read banking (4 way) with 4 operand instructions

- FAMA as in FUSED ADD MULTIPLY ADD, introduce a pre adder

- e = (a + b) * c + d ... fama(a,b,c,d)

- This enables single instruction lerp(a,b,c) := (b-a)*c+a assuming no precision loss

- Along with single instruction bool logic: Gtz(), Ltz(), Ne(), Sel() := lerp(), etc

- Or3(x,y,z) ... saturate(fama(x,y,1.0,z))

- etc

________________________________________________________________________________________________________________________________

[GPU] Log Depth Encoding

For reference...

// LOG DEPTH ENCODING

// ==================

// - Don't need too much precision around the minimum traversable coordinate

// - Or alternatively can clip on near plane

// - This logic improves precision by a good amount (1/118 to 1/174)

// - When s=2047, n=256, a=1/256, m=2^25

// - Encoding: x=log2(z*a+(1-a*n))*b -> {0 to s}

// - m ... maximum depth value that can be encoded

// - n ... minimum depth value that can be encoded

// - s ... maximum step value

// - z ... {0 to m}

// - a ... controls distribution close to zero

// - b ... s/log2(m*a+1-n*a)

// - Decoding: z=exp2(x*(1/b))*(1/a)+(n-(1/a))

Why not just mask part of a FP16 value and use that instead of log depth encoding?

Float Toy

// - Breakdown

// fedcba9876543210

// ================

// s............... sign (ignore)

// .eeeee.......... exponent (don't want top bit, due to wasted enocding)

// ......mmmmmmmmmm mantissa

// ----------------

// ..eeeemmmmmmm... possible encoding for simple masking

// ..11111111111... 1.993 (around 2)

// ..00000000001... 4.8e-7 (around 1/2M)

// - Using simple masking burns roughly 1/16 of encoding in a linear region

// - Complex masking can only approach 1/32 of encoding

// - This neglects lower 3-bits of precision (gets worse if including more bits)

// - So NO!

________________________________________________________________________________________________________________________________

[GPU] Ultimate Video Quality

- Very Few Dispatches Each Frame -

CPU is doing effectively nothing. All the game logic is on the GPU.

- Input Sampled on the GPU -

Background CPU thread is pushing latest input to GPU readable buffer.

GPU is reading CPU input and generating camera translational update right before view-dependent rendering.

- Camera Rotation Independent Rendering -

Scene is rendered initially into an Octahedron.

This rendering is dependent on camera translation but not camera angle.

GPU is reading CPU input again and generating camera rotation update right before final view-angle-dependent rendering,

which takes the octahedral space and generates the cylindrical projection the user sees.

- V-Sync is ON -

This is the only way to ensure consistent motion is visually consistent in time.

TERMS

=========

latency ... as in input read on GPU to start of first frame's line on CRT (ignoring H blanking)

gi ........ GPU view independent work

gd ........ GPU view translation dependent work

gc ........ GPU view camera angle dependent work

MAXED OUT GPU

==================

/_gi5_/_gd5_/_gc5_//_gi6_/_gd6_/_gc6_//_gi7_/_gd7_/_gc7_/

[____scanout_4____][____scanout_5____][____scanout_6____]

^ ^ ^

| |<---->| ... Camera rotation latency (slightly lower)

| |

|<---------->| ... Camera translation and button to flash latency (slightly higher)

MAXED OUT GPU - LATENCY INDEPENDENT OF CPU WORK

===================================================

(_cpu6_) (_cpu7_) (_cpu8_)

/_gi5_/_gd5_/_gc5_//_gi6_/_gd6_/_gc6_//_gi7_/_gd7_/_gc7_/ -+

[____scanout_4____][____scanout_5____][____scanout_6____] |

|

or |- same latency

|

(_cpu6_) (_cpu7_) (_cpu8_) |

/_gi5_/_gd5_/_gc5_//_gi6_/_gd6_/_gc6_//_gi7_/_gd7_/_gc7_/ -+

[____scanout_4____][____scanout_5____][____scanout_6____]

NON-MAXED OUT GPU - LATENCY DEPENDENT ON WHEN GPU WORK STARTS

=================================================================

/_gi5_/_gd5_/_gc5_/ /_gi6_/_gd6_/_gc6_/ /_gi7_/_gd7_/_gc7_/

[________scanout_4________][________scanout_5________][________scanout_6________]

^ ^ ^

| |<---->|

| | ... Lower latency

|<---------->|

vs

/_gi5_/_gd5_/_gc5_/ /_gi6_/_gd6_/_gc6_/ /_gi7_/_gd7_/_gc7_/

[________scanout_4________][________scanout_5________][________scanout_6________]

^ ^ ^

| |<------------>|

| | ... Higher latency

|<------------------>|

________________________________________________________________________________________________________________________________

[GPU] Unlimited Boy

Fantasy console inspired by the 160x144 pixel and 4 shades of grey Gameboy...

Unlimited Boy Concept

- Push up to 256x128 = 32768 pixels (Letterboxed NES, better for modern 16:9 displays)

- Push up to 3-bit/pixel (8 shade monochome)

- Separate sprite mask from sprite, so sprite can use all 8 shades

- Sprite uses 4 bit planes {mask, high bit, med bit, low bit}

- 8x4 bit plane in one 32-bit integer, full 8x4 sprite in a 16-byte 'uvec4' (single load)

- Get 64 million sprites in 1 GiB of buffer memory (uncompressed)

- Can fetch a sprite into K$ using one S_LOAD_DWORDX4 operation

- ----

- 64 lane workgroup = 32x1 pixels / lane = 256x8 pixel row

- 16 workgroups / screen ... not enough to fill GPU

- Each workgroup working on a subset of the "unlimited" sprite list

- Ordered composite of workgroups at end

- ----

- Workgroup works on a sprite at a time

- Each lane has 4 uints (one per bit plane) for 32x1 pixels

- Extract the associated 8x1 line from sprite for the 4 planes

- Shift and mask, then compsite with logic ops

- ----

- Can burn sprites for various things (effectively unlimited memory)

- Like have sub-pixel shift sprites (4 sprites = 2x2, or 16 sprites = 4x4)

- Or different brightness, rotation angles, scaling, etc

- ----

- Without using extra sprite memory, could introduce dither mask modifier

- Enables a sprite to have dithered 'transparency'

- Could then split sprites into N copies, each with different 'dither'

- Where all the dithers add up to the origional sprite

- So that Z ordered sprites won't have pop, because the 'sprite' is split into N layers

- So as sprites occupy similar Z they blend together

________________________________

[PRG] Links

________________________________________________________________________________________________________________________________

[PRG] Lottes6x16 Font

A Bitmap Terminal Font

Designed for monospace text editing.

Lottes6x16.fon - Easy to find for general app usage like in Notepad2.

LottesTerminal6x16.fon - Special version to make work in windows terminal.

As a programmer who sticks to 1080p displays, I use this bitmap font for source editing and windows terminal.

The font was made using Fony.

Right click on the file and "Install" to install.

Use "6x16" in the terminal.

________________________________________________________________________________________________________________________________

[PRG] Page Warming

Something From an Existing 'C' Engine ...

The desire for the user is to have a hitch-free experience.

OS design today seems more around bloatware, not designed for tiny tight binaries.

The problem being that pages are not necessarily there until needed,

and that process can be a latency chain nightmare (hitch fest).

To workaround this problem, on program launch, and repeated each time the app gets focus, a background thread walks all pages.

- Code is warmed first, with simple read of the first word of each 4K page.

- Data is warmed next, with an atomic ADD of a loaded zero of the first word of each 4K page.

The atomic forces initially zero-fill pages to be converted from the common zero-fill page to a unique dedicated page.

The 'loaded zero' (unknown at compile time) is done to make sure a smart compiler cannot factor out the atomic operation.

All code is done with ROM_ defined to 1, the source file simply includes itself, wrapped with beginning WrmBas() and ending WrmEnd() functions

so it becomes possible to easily know the range of addresses for code.

#define ROM_ 1

S_ void WrmBas(void){Crash();}

#include "nvg0.c"

S_ void WrmEnd(void){Crash();}

#undef ROM_

All data is placed into one structure (with RAM_ defined to 1, source including itself), so finding start and end is easy.

#define RAM_ 1

typedef struct{

#include "nvg0.c"

A_(64) I1 end[1024*1024/4];}RamT;S_ A_(64) L1 ramM[sizeof(RamT)/8];

#define ramR TR_(RamT,L1_(ramM))

#define ramV TV_(RamT,L1_(ramM))

#undef RAM_

________________________________________________________________________________________________________________________________

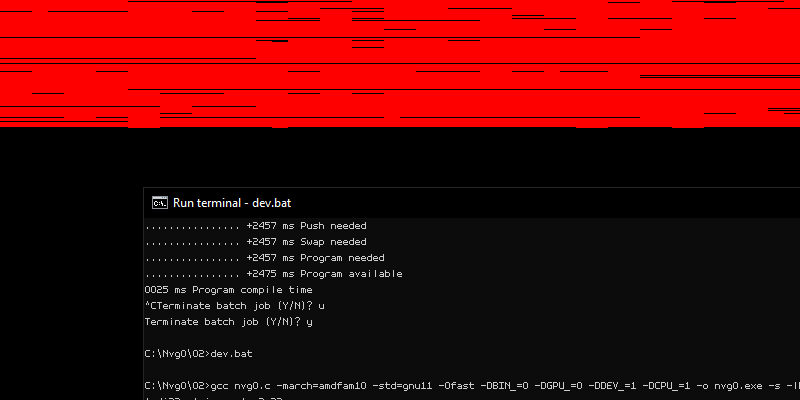

[PRG] Self Modifying Binary

Single File App

Turns out this still works in Win10. But is likely to not work in the future (for another post).

The concept is simple,

instead of having a binary and data file(s),

just have a binary,

where the application saves it's configuration state directly into the binary.

Or the step beyond, saving a RAM snapshot into the binary,

so the application can easily startup where it last left off,

and the user can have any number of save points by having different binaries.

Distribution and install of the application is just place the file wherever you want to run it from.

Uninstall is just delete the binary.

Very easy setup, no registry or config file garbage.

The technique is quite simple.

- When the binary starts it copies itself to a temp file, then launches the temp file, then exits.

- The temp file launch runs the application.

- Temp file launch is free to modify the original binary (which is no longer running).

Not shown below, but on exit, the temp file launch could launch the original binary with a command to delete the temp file.

This would work to automatically not leave a garbage file around.

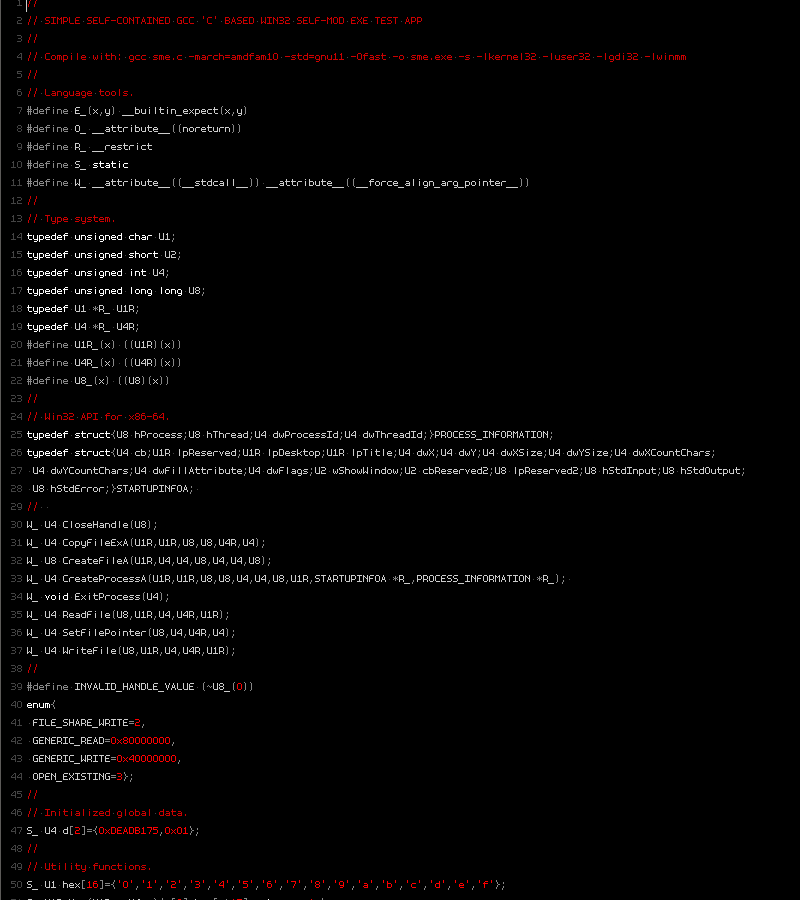

Proof of Concept

//

// SIMPLE SELF-CONTAINED GCC 'C' BASED WIN32 SELF-MOD EXE TEST APP

//

// Compile with: gcc sme.c -march=amdfam10 -std=gnu11 -Ofast -o sme.exe -s -lkernel32 -luser32 -lgdi32 -lwinmm

//

// Language tools.

#define E_(x,y) __builtin_expect(x,y)

#define O_ __attribute__((noreturn))

#define R_ __restrict

#define S_ static

#define W_ __attribute__((__stdcall__)) __attribute__((__force_align_arg_pointer__))

//

// Type system.

typedef unsigned char U1;

typedef unsigned short U2;

typedef unsigned int U4;

typedef unsigned long long U8;

typedef U1 *R_ U1R;

typedef U4 *R_ U4R;

#define U1R_(x) ((U1R)(x))

#define U4R_(x) ((U4R)(x))

#define U8_(x) ((U8)(x))

//

// Win32 API for x86-64.

typedef struct{U8 hProcess;U8 hThread;U4 dwProcessId;U4 dwThreadId;}PROCESS_INFORMATION;

typedef struct{U4 cb;U1R lpReserved;U1R lpDesktop;U1R lpTitle;U4 dwX;U4 dwY;U4 dwXSize;U4 dwYSize;U4 dwXCountChars;

U4 dwYCountChars;U4 dwFillAttribute;U4 dwFlags;U2 wShowWindow;U2 cbReserved2;U8 lpReserved2;U8 hStdInput;U8 hStdOutput;

U8 hStdError;}STARTUPINFOA;

//

W_ U4 CloseHandle(U8);

W_ U4 CopyFileExA(U1R,U1R,U8,U8,U4R,U4);

W_ U8 CreateFileA(U1R,U4,U4,U8,U4,U4,U8);

W_ U4 CreateProcessA(U1R,U1R,U8,U8,U4,U4,U8,U1R,STARTUPINFOA *R_,PROCESS_INFORMATION *R_);

W_ void ExitProcess(U4);

W_ U4 ReadFile(U8,U1R,U4,U4R,U1R);

W_ U4 SetFilePointer(U8,U4,U4R,U4);

W_ U4 WriteFile(U8,U1R,U4,U4R,U1R);

//

#define INVALID_HANDLE_VALUE (~U8_(0))

enum{

FILE_SHARE_WRITE=2,

GENERIC_READ=0x80000000,

GENERIC_WRITE=0x40000000,

OPEN_EXISTING=3};

//

// Initialized global data.

S_ U4 d[2]={0xDEADB175,0x01};

//

// Utility functions.

S_ U1 hex[16]={'0','1','2','3','4','5','6','7','8','9','a','b','c','d','e','f'};

S_ U1R Hex(U1R a,U4 v){a[0]=hex[v&15];return a+1;}

S_ U1R HexU1(U1R a,U4 v){Hex(a,v>>4);Hex(a+1,v);return a+2;}

S_ U1R HexU2(U1R a,U4 v){HexU1(a,v>>8);HexU1(a+2,v);return a+4;}

//

// Entry point.

O_ void main(U4 argc,U1R *R_ argv){

// If not called with arguments (base 'sme.exe' launch).

if(argc!=2){

// Copy 'sme.exe' to 'sme-cpy.exe'.

U4 c[1];CopyFileExA(U1R_("sme.exe"),U1R_("sme-cpy.exe"),0,0,U4R_(c),0);

// Launch 'sme-cpy.exe 1'.

S_ STARTUPINFOA si;

S_ PROCESS_INFORMATION pi;

si.cb=sizeof(STARTUPINFOA);

CreateProcessA(0,U1R_("sme-cpy.exe 1"),0,0,1,0,0,0,&si,&pi);

// Exit the process.

ExitProcess(0);}

// Called with arguments (the 'sme-cpy.exe 1' launch).

// Open access to standard output into console.

U8 f=CreateFileA(U1R_("CONOUT$"),GENERIC_WRITE,FILE_SHARE_WRITE,0,OPEN_EXISTING,0,0);

// Write out value after 0xDEADB175 to console.

U1 b[4]={'.','.','\n',0};HexU1(b,d[1]);

U4 r[1];WriteFile(f,U1R_(b),4,U4R_(r),0);

// Open 'sme.exe' for R/W, loop until this succeeds (just in case 'sme.exe' is still open for execute).

U8 h;while(1){h=CreateFileA(U1R_("sme.exe"),GENERIC_WRITE|GENERIC_READ,FILE_SHARE_WRITE,0,OPEN_EXISTING,0,0);

if(h!=INVALID_HANDLE_VALUE)break;}

// Read 'sme.exe' into memory, using something dumb (know file size is under 64 KiB).

S_ U4 m[16384];

ReadFile(h,U1R_(m),65536,U4R_(r),0);

// Find 0xDEADB175 offset (know this happens to be U4 aligned).

U4 o=0;while(o<16380){if(m[o]==0xDEADB175)break;o++;}o=o*4+4;

// Write out offset to console.

U1 b2[6]={'.','.','.','.','\n',0};HexU2(b2,o);

WriteFile(f,U1R_(b2),6,U4R_(r),0);

// Increment value after 0xDEADB175.

d[1]++;

// Write updated value to 'sme.exe'.

SetFilePointer(h,o,0,0);

WriteFile(h,U1R_((d+1)),4,U4R_(r),0);

// Close the file.

CloseHandle(h);

// Exit the process.

while(1)ExitProcess(0);}

________________________________________________________________________________________________________________________________

[PRG] PE Binary Header

PE

Building a simple 64-bit binary from scratch.

References.

Unfortunately Win 10 breaks compatibility with the small PE tricks which worked on Win 7 and prior.

Since I don't want to do my own custom importer

(due to the risk of Win 10 breaking that compatibility as well),

there is a gap of 5 cachelines between initial file headers and imports.

Overall this burns 5 cachelines total for headers and imports.

This is 80:1 bloat factor required to get a binary executing on Windows.